VHDL je zkratka pro velmi high-speed integrated circuit hardware description language. Jedná se o programovací jazyk používaný k modelování digitálního systému dataflow, behaviorální a strukturální styl modelování. Tento jazyk byl poprvé představen v roce 1981 pro ministerstvo obrany (DoD) v rámci programu VHSIC.

popisující návrh

ve VHDL se entita používá k popisu hardwarového modulu. Entitu lze popsat pomocí,

- Entity declaration

- Architecture

- Configuration

- package declaration

- Package body

podívejme se, co to je?

Entity Declaration

definuje názvy, vstupní výstupní signály a režimy hardwarového modulu.

syntaxe−

entity entity_name is Port declaration;end entity_name;

prohlášení entity by mělo začínat slovy „entita“ a končit klíčovými slovy „konec“. Směr bude vstup, výstup nebo výstup.

| V | Port lze číst |

| Port může být napsán | |

| Inout | Port lze číst a zapisovat |

| Vyrovnávací paměti | Port lze číst a zapisovat, to může mít jen jeden zdroj. |

Architektura –

architekturu lze popsat pomocí strukturálního, datového toku, behaviorálního nebo smíšeného stylu.

syntaxe−

architecture architecture_name of entity_name architecture_declarative_part;begin Statements;end architecture_name;

zde bychom měli určit název entity, pro kterou píšeme tělo architektury. Prohlášení o architektuře by měla být uvnitř klíčových slov „begin“ a „éld“. Deklarativní část architektury může obsahovat proměnné, konstanty nebo deklaraci komponent.

modelování toku dat

v tomto stylu modelování je tok dat entitou vyjádřen pomocí souběžného (paralelního) signálu. Souběžné příkazy ve VHDL jsou kdy a generovat.

kromě nich přiřazení pouze pomocí operátorů (a ne +,*, sll atd.) lze také použít k vytvoření kódu.

konečně lze v tomto druhu kódu použít také speciální druh přiřazení, nazývaný blok.

V současné kód, následující mohou být použity−

- Operátory

- KDYŽ prohlášení (KDYŽ/JINAK nebo S/SELECT/KDY);

- VYTVOŘIT prohlášení;

- BLOK prohlášení

Behaviorální Modelování

V tomto modelování styl, chování subjektu jako sada příkazů je provedena postupně v určeném pořadí. Pouze příkazy umístěné uvnitř procesu, funkce nebo procedury jsou sekvenční.

procesy, funkce a procedury jsou jediné části kódu, které jsou prováděny postupně.

nicméně jako celek je některý z těchto bloků stále souběžný s jinými příkazy umístěnými mimo něj.

jedním z důležitých aspektů kódu chování je, že není omezen na sekvenční logiku. Ve skutečnosti s ním můžeme stavět sekvenční obvody i kombinační obvody.

příkazy chování jsou IF, WAIT, CASE a LOOP. Proměnné jsou také omezeny a mají být použity pouze v sekvenčním kódu. Proměnná nikdy nemůže být globální, takže její hodnotu nelze přímo předávat.

strukturální modelování

v tomto modelování je entita popsána jako soubor vzájemně propojených komponent. Příkaz instance komponenty je souběžný příkaz. Pořadí těchto prohlášení proto není důležité. Strukturální styl modelování popisuje pouze propojení komponent (považovaných za černé skříňky), aniž by naznačoval jakékoli chování samotných komponent ani entity, kterou společně reprezentují.

Ve Strukturálním modelování, architekturu tělo se skládá ze dvou částí − deklarativní část (před klíčové slovo begin) a prohlášení část (po klíčové slovo begin).

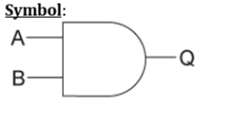

Logické Operace – A BRÁNY

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

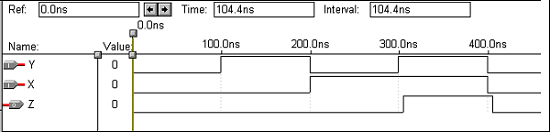

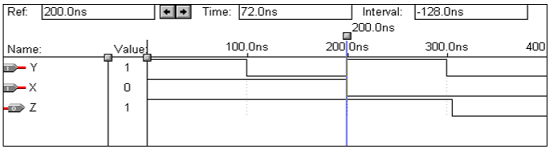

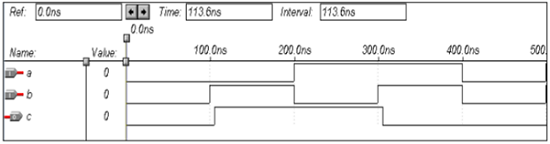

Průběhy

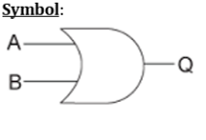

Logické Operace – NEBO Brány

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Průběhy

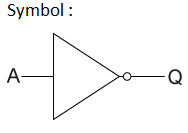

Logické Operace – NE Brány

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

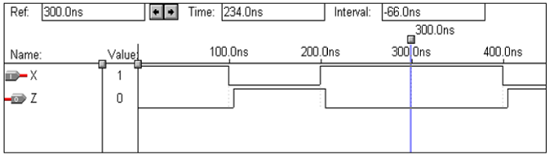

Průběhy

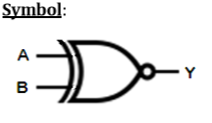

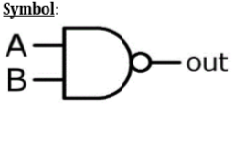

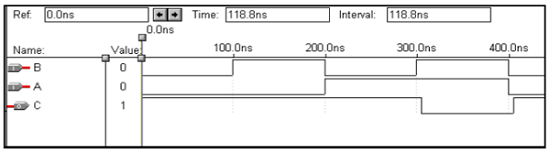

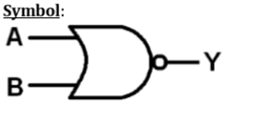

Logické Operace – NAND Gate

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Průběhy

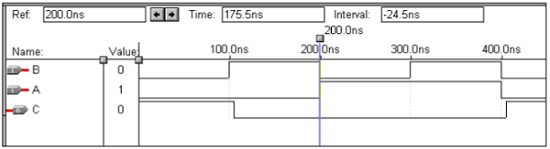

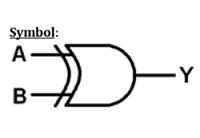

Logické Operace – ANI Bránu

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Průběhy

Logické Operace – XOR Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Průběhy

Logické Operace – X-ANI Brány