VHDL signifie langage de description de matériel de circuit intégré à très grande vitesse. C’est un langage de programmation utilisé pour modéliser un système numérique par flux de données, style de modélisation comportemental et structurel. Ce langage a été introduit pour la première fois en 1981 pour le département de la Défense (DoD) dans le cadre du programme VHSIC.

Description d’une conception

En VHDL, une entité est utilisée pour décrire un module matériel. Une entité peut être décrite en utilisant,

- Déclaration d’entité

- Architecture

- Configuration

- Déclaration de package

- Corps de package

Voyons quelles sont-elles ?

Déclaration d’entité

Elle définit les noms, les signaux d’entrée et de sortie et les modes d’un module matériel.

Syntaxe −

entity entity_name is Port declaration;end entity_name;

Une déclaration d’entité doit commencer par « entité » et se terminer par les mots clés « fin ». La direction sera entrée, sortie ou inout.

| Dans le port | peut être lu |

| Le port Out | peut être écrit |

| Le port Inout | peut être lu et écrit |

| Le port Buffer | peut être lu et écrit, il ne peut avoir qu’une seule source. |

Architecture –

L’architecture peut être décrite en utilisant un style structurel, de flux de données, comportemental ou mixte.

Syntaxe −

architecture architecture_name of entity_name architecture_declarative_part;begin Statements;end architecture_name;

Ici, nous devons spécifier le nom de l’entité pour laquelle nous écrivons le corps de l’architecture. Les instructions d’architecture doivent être à l’intérieur des mots clés » begin » et » énd « . La partie déclarative de l’architecture peut contenir des variables, des constantes ou une déclaration de composant.

Modélisation du flux de données

Dans ce style de modélisation, le flux de données à travers l’entité est exprimé à l’aide d’un signal simultané (parallèle). Les instructions simultanées en VHDL sont WHEN et GENERATE.

En plus d’eux, les affectations utilisant uniquement des opérateurs (ET NON & plus;, *, sll, etc.) peut également être utilisé pour construire du code.

Enfin, un type spécial d’affectation, appelé BLOC, peut également être utilisé dans ce type de code.

Dans le code concurrent, les éléments suivants peuvent être utilisés −

- Opérateurs

- L’instruction WHEN (WHEN/ELSE ou AVEC /SELECT/WHEN) ;

- L’instruction GENERATE ;

- L’instruction BLOCK

Modélisation comportementale

Dans ce style de modélisation, le comportement d’une entité en tant qu’ensemble d’instructions est exécuté séquentiellement dans l’ordre spécifié. Seules les instructions placées dans un PROCESSUS, une FONCTION ou une PROCÉDURE sont séquentielles.

LES PROCESSUS, FONCTIONS et PROCÉDURES sont les seules sections de code exécutées séquentiellement.

Cependant, dans son ensemble, l’un de ces blocs est toujours concurrent de toute autre instruction placée en dehors de celui-ci.

Un aspect important du code de comportement est qu’il ne se limite pas à la logique séquentielle. En effet, avec elle, nous pouvons construire des circuits séquentiels ainsi que des circuits combinatoires.

Les instructions de comportement sont IF, WAIT, CASE et LOOP. Les VARIABLES sont également restreintes et elles sont censées être utilisées uniquement dans le code séquentiel. La VARIABLE ne peut jamais être globale, sa valeur ne peut donc pas être transmise directement.

Modélisation structurelle

Dans cette modélisation, une entité est décrite comme un ensemble de composants interconnectés. Une instruction d’instanciation de composant est une instruction concurrente. Par conséquent, l’ordre de ces déclarations n’est pas important. Le style structurel de modélisation ne décrit qu’une interconnexion de composants (considérés comme des boîtes noires), sans impliquer aucun comportement des composants eux-mêmes ni de l’entité qu’ils représentent collectivement.

Dans la modélisation structurelle, le corps de l’architecture est composé de deux parties : la partie déclarative (avant le début du mot−clé) et la partie instruction (après le début du mot-clé).

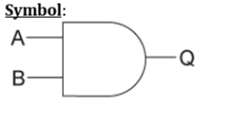

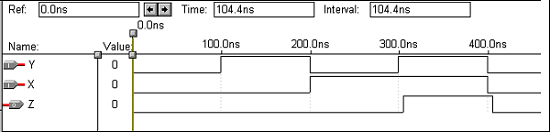

Opération logique ET PORTE

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

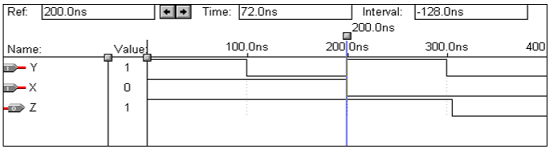

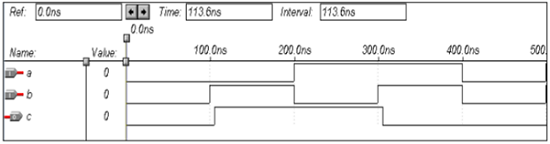

Formes d’onde

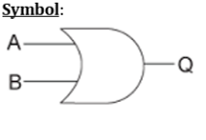

Opération OU Porte logique

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Formes d’onde

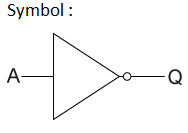

Fonctionnement logique – PAS de porte

| X | A |

|---|---|

| 0 | 1 |

| 1 | 0 |

Formes d’onde

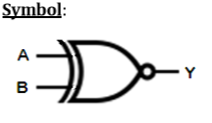

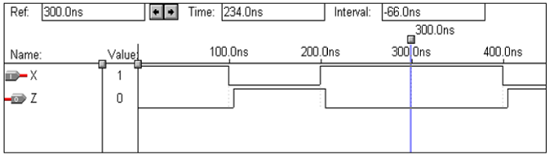

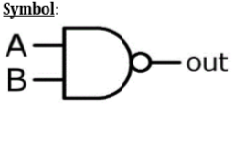

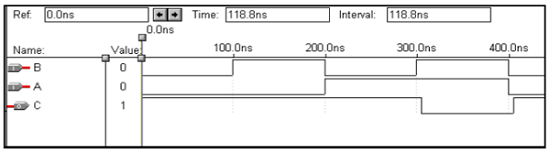

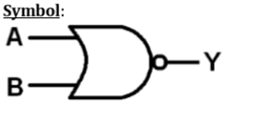

Opération logique – Porte NAND

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Formes d’onde

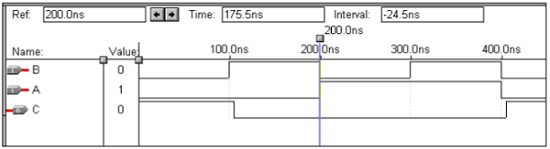

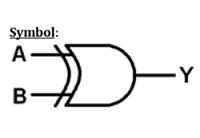

Opération logique – Porte NOR

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Formes d’onde

Opération logique – Porte XOR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Formes d’onde

Opération logique – Porte X-NOR