La discussion sur la prochaine génération de mémoire DDR s’est intensifiée ces derniers mois, les fabricants présentant une grande variété de véhicules d’essai avant le lancement complet du produit. Les plates-formes qui prévoient d’utiliser la DDR5 approchent également à grands pas, avec des débuts attendus du côté de l’entreprise avant de se répercuter lentement sur le consommateur. Comme pour toutes ces choses, le développement se fait par étapes: contrôleurs de mémoire, interfaces, IP de test équivalent électrique et modules. C’est cette dernière étape que SK Hynix lance aujourd’hui, ou du moins les puces qui entrent dans ces modules.

DDR5 est la prochaine étape de la mémoire de plate-forme pour une utilisation dans la majorité des grandes plates-formes de calcul. La spécification (publiée en juillet 2020) réduit la tension principale de 1,2 V à 1,1 V, augmente la densité maximale des matrices en silicium d’un facteur 4, double le débit de données maximal, double la longueur de rafale et double le nombre de groupes de banques. En termes simples, les spécifications DDR de JEDEC permettent un module sans tampon de 128 Go fonctionnant à la norme DDR5-6400. Les RDIMM et les LRDIMM devraient pouvoir aller beaucoup plus haut, si la puissance le permet.

Il existe quatre angles dans le monde de la DDR sur lesquels toutes les personnes impliquées dans la spécification souhaitent itérer. La capacité est évidente, mais la bande passante mémoire joue également un rôle clé dans la mise à l’échelle des performances des charges de travail multicœurs courantes dans les grands serveurs à nombre de cœurs que nous voyons. Les deux autres sont la puissance (un objectif évident), et l’autre est la latence, une autre mesure clé pour les performances.

Avec la DDR5, l’un des principaux changements pour aider à conduire ceci est la façon dont la mémoire est vue par le système. Plutôt que d’être un seul canal de données 64 bits par module, la DDR5 est considérée comme deux canaux de données 32 bits par module (ou 40 bits en ECC). La longueur de rafale a doublé, ce qui signifie que chaque canal 32 bits fournira toujours 64 octets par opération, mais peut le faire de manière plus entrelacée. Cela signifie que le système standard DDR4 à deux canaux 64 bits se transformera en un arrangement DDR5 à quatre canaux 32 bits, bien que chaque clé mémoire fournisse un total de 64 bits, mais de manière plus contrôlable. Cela facilite également le doublement du débit de données, un élément clé pour augmenter la bande passante maximale, ainsi qu’une fonction d’actualisation de banque plus fine, qui permet des opérations asynchrones sur la mémoire pendant son utilisation, réduisant ainsi la latence.

La régulation de tension est également déplacée de la carte mère vers le module de mémoire, ce qui permet au module de réguler ses propres besoins. Nous avons déjà vu DDR4 adopter un contrôle Vdroop par puce, mais cela pousse l’idée un peu plus loin pour un contrôle et une gestion plus stricts de la puissance. Il met également la gestion de l’alimentation entre les mains du fournisseur du module plutôt que du fabricant de la carte mère, ce qui permet au fabricant du module de dimensionner ce qui est nécessaire pour une mémoire plus rapide – il sera intéressant de voir comment différents micrologiciels font face à une mémoire de jeu standard non JEDEC qui dépassera sans aucun doute les spécifications.

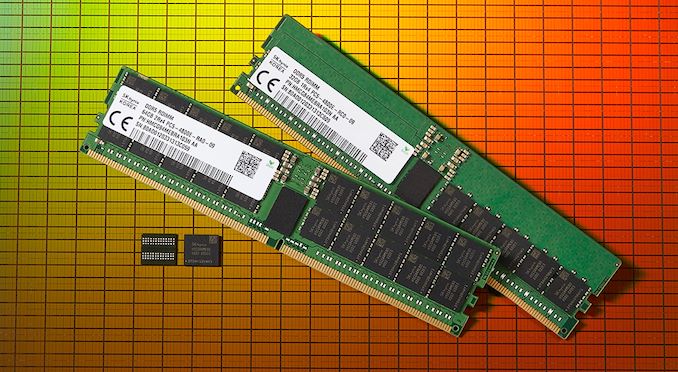

L’annonce de SK Hynix aujourd’hui est qu’ils sont prêts à commencer à expédier de la mémoire ECC DDR5 aux fabricants de modules, en particulier des matrices 16 gigabits construites sur son processus 1Ynm qui prennent en charge la DDR5–4800 à la DDR5-5600 à 1,1 volts. Avec la bonne technologie d’emballage (telle que le TSV 3D), SK Hynix affirme que les partenaires peuvent construire des LRDIMM de 256 Go. Un binning supplémentaire des puces pour des vitesses supérieures à celles de JEDEC devra être effectué par les fabricants de modules eux-mêmes. SK Hynix semble également avoir ses propres modules, en particulier des RDIMM 32 Go et 64 Go à la DDR5-4800, et a déjà promis d’offrir de la mémoire jusqu’à la DDR5-8400.

SK Hynix n’a pas fourni d’informations sur les sous-horaires de ces modules. La spécification JEDEC définit trois modes différents pour la DDR5-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B : 40-40-40

- DDR5-4800C: 42-42-42

On ne sait pas lequel de ceux-ci est utilisé par SK Hynix. Le module dit ‘4800E’, mais cela semble faire partie de la dénomination du module, car la spécification JEDEC ne dépasse pas une valeur CL de 42 pour DDR5-4800.

Pour la bande passante, d’autres fabricants de mémoire ont cité que pour les 38, 4 Go / s théoriques que chaque module de DDR5-4800 peut apporter, ils voient déjà des nombres effectifs dans la plage de 32 Go / s. C’est au-dessus des 20-25 GB / s effectifs par canal que nous voyons sur DDR4-3200 aujourd’hui. D’autres fabricants de mémoires ont déjà annoncé qu’ils échantillonnaient de la DDR5 avec des clients depuis le début de l’année.

Dans le cadre de l’annonce, il était intéressant de voir Intel comme l’un des principaux partenaires de ces modules. Intel s’est engagé à activer la DDR5 sur sa plate-forme de processeur Sapphire Rapids Xeon, dont le lancement initial est prévu fin 2021/2022. AMD n’a pas été mentionné avec l’annonce, et aucun partenaire Arm non plus.

Selon SK Hynix, la DDR5 devrait représenter 10 % du marché mondial en 2022, pour atteindre 43 % en 2024. Le point d’intersection pour les plates-formes grand public est quelque peu flou à ce stade, car nous ne sommes probablement qu’à mi-chemin (ou moins de la moitié) du cycle DDR4. Traditionnellement, nous nous attendons à une interception des coûts entre l’ancienne et la nouvelle technologie lorsqu’elles sont égales en parts de marché, mais les coûts supplémentaires de régulation de la tension requis par la DDR5 risquent d’augmenter les coûts des modules – de la livraison de puissance standard sur les modules JEDEC à une solution plus robuste sur les modules overclockés. Cela devrait cependant rendre les cartes mères moins chères à cet égard.

Source: SK hynix

Lecture connexe

- Spécification de la mémoire DDR5 Publiée: Préparer le terrain pour la DDR5-6400 Et au-delà

- SK Hynix: Nous prévoyons pour la DDR5-8400 à 1.1 Volts

- Mise à jour de la cadence DDR5: Lancement à 4800 MT / s, Plus de 12 SOC DDR5 en développement

- Samsung produira de la DDR5 en 2021 (avec EUV)

- Voici quelques DDR5-4800: Premier coup d’œil pratique à la DRAM Next Gen

- CES 2020: Micron Commence à Exemple de RDIMM DDR5 avec des partenaires Serveurs

- SK Hynix Détails DDR5-6400

- Keysight Révèle les Tests DDR5 & Système de validation

- SK Hynix Développe La Première Puce de Mémoire DDR5-5200 de 16 Go, Démos DDR5 RDIMM

- Cadence & Micron Mise à jour DDR5: Puces de 16 Go en bonne voie pour 2019

- Démo de Cadence et Micron DDR5-4400 IMC et mémoire, Attendue en 2019