La discussione sulla prossima generazione di memoria DDR è stata aflutter negli ultimi mesi in quanto i produttori hanno presentato un’ampia varietà di veicoli di prova prima di un lancio completo del prodotto. Anche le piattaforme che prevedono di utilizzare DDR5 si stanno avvicinando rapidamente, con un debutto previsto sul lato aziendale prima di scivolare lentamente verso il consumatore. Come con tutte queste cose, lo sviluppo arriva in fasi: controller di memoria, interfacce, test IP equivalenti elettrici e moduli. È quella fase finale che SK Hynix sta lanciando oggi, o almeno i chip che vanno in questi moduli.

DDR5 è la fase successiva della memoria della piattaforma per l’uso nella maggior parte delle principali piattaforme di calcolo. La specifica (rilasciata a luglio 2020) riduce la tensione principale da 1,2 V a 1,1 V, aumenta la densità massima dello stampo di silicio di un fattore 4, raddoppia la velocità massima dei dati, raddoppia la lunghezza di scoppio e raddoppia il numero di gruppi bancari. In poche parole, le specifiche JEDEC DDR consentono un modulo senza buffer da 128 GB in esecuzione su DDR5-6400. RDIMM e LRDIMM dovrebbero essere in grado di andare molto più in alto, potenza permettendo.

Ci sono quattro angoli nel mondo della DDR che tutti coloro che sono coinvolti nella specifica vogliono scorrere. La capacità è quella ovvia, ma anche la larghezza di banda della memoria gioca un ruolo chiave nel ridimensionamento delle prestazioni dei carichi di lavoro multi-core comuni nei grandi server core-count che stiamo vedendo. Gli altri due sono il potere (un obiettivo ovvio) e l’altro è la latenza, un’altra metrica chiave per le prestazioni.

Con DDR5, uno dei principali cambiamenti per aiutare a guidare questo è il modo in cui la memoria è vista dal sistema. Piuttosto che essere un singolo canale dati a 64 bit per modulo, DDR5 è visto come due canali dati a 32 bit per modulo (o 40 bit in ECC). La lunghezza di burst è raddoppiata, il che significa che ogni canale a 32 bit fornirà ancora 64 byte per operazione, ma può farlo in modo più interlacciato. Ciò significa che il sistema standard “due canali DDR4 a 64 bit” si trasformerà in una disposizione “quad 32-bit channel DDR5”, sebbene ogni memory stick fornisca un totale di 64 bit ma in un modo più controllabile. Questo rende anche raddoppiando la velocità di trasmissione dati, un elemento chiave per aumentare la larghezza di banda di picco, più facile, così come una funzione di aggiornamento banca grana più fine, che consente operazioni asincrone sulla memoria mentre è in uso, riducendo la latenza.

Anche la regolazione della tensione viene spostata dalla scheda madre al modulo di memoria, consentendo al modulo di regolare le proprie esigenze. Abbiamo già visto DDR4 adottare un controllo Vdroop per chip, ma questo porta l’intera idea a un ulteriore passo avanti per un controllo e una gestione della potenza più stretti. Mette anche la gestione dell’alimentazione nelle mani del fornitore del modulo piuttosto che del produttore della scheda madre, consentendo al produttore del modulo di ridimensionare ciò che è necessario per una memoria più veloce-sarà interessante vedere come i diversi firmware affrontano la memoria di gioco standard non JEDEC che senza dubbio andrà al di sopra delle specifiche.

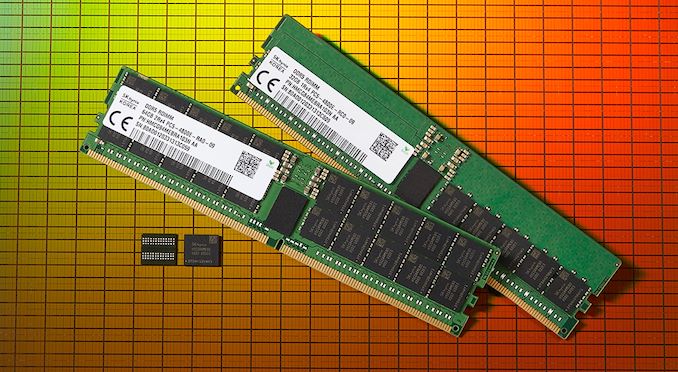

L’annuncio di SK Hynix oggi è che sono pronti per iniziare a spedire la memoria DDR5 ECC ai produttori di moduli, in particolare 16 gigabit dies costruiti sul suo processo 1Ynm che supportano DDR5-4800 a DDR5-5600 a 1.1 volt. Con la giusta tecnologia di imballaggio (come 3D TSV), SK Hynix dice che i partner possono costruire 256 GB LRDIMM. Il binning aggiuntivo dei chip per velocità migliori di JEDEC dovrà essere fatto dagli stessi produttori di moduli. SK Hynix sembra anche avere i propri moduli, in particolare 32GB e 64GB RDIMM a DDR5-4800, e in precedenza ha promesso di offrire memoria fino a DDR5-8400.

SK Hynix non ha fornito informazioni sui tempi secondari di questi moduli. La specifica JEDEC definisce tre diverse modalità per DDR5-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B: 40-40-40

- DDR5-4800C: 42-42-42

Non è chiaro quale di questi sta usando SK Hynix. Il modulo dice ‘4800E’, tuttavia sembra essere solo parte della denominazione del modulo, poiché la specifica JEDEC non va oltre un valore CL di 42 per DDR5-4800.

Per la larghezza di banda, altri produttori di memoria hanno citato che per i teorici 38.4 GB/s che ogni modulo di DDR5-4800 può portare, stanno già vedendo numeri effettivi nell’intervallo 32 GB/s. Questo è al di sopra dell’effettivo 20-25 GB/s per canale che stiamo vedendo su DDR4-3200 oggi. Altri produttori di memoria hanno già annunciato che stanno campionando DDR5 con i clienti dall’inizio dell’anno.

Come parte dell’annuncio, è stato interessante vedere Intel come uno dei partner principali per questi moduli. Intel si è impegnata ad abilitare DDR5 sulla sua piattaforma di processori Sapphire Rapids Xeon, prevista per il lancio iniziale alla fine del 2021/2022. AMD non è stata menzionata con l’annuncio e nessuno dei partner Arm.

SK Hynix cita che DDR5 dovrebbe essere il 10% del mercato globale nel 2022, aumentando al 43% nel 2024. Il punto di intersezione per le piattaforme consumer è un po ‘ sfocato a questo punto, poiché probabilmente siamo solo a metà (o meno della metà) del ciclo DDR4. Tradizionalmente ci aspettiamo un’intercettazione dei costi tra la vecchia e la nuova tecnologia quando sono uguali in quota di mercato, tuttavia i costi aggiuntivi nella regolazione della tensione che DDR5 richiede probabilmente aumenteranno i costi dei moduli, scalando dall’erogazione di potenza standard sui moduli JEDEC fino a una soluzione più robusta sui moduli overcloccati. Dovrebbe tuttavia rendere le schede madri più economiche a questo proposito.

Fonte: SK hynix

Related Reading

- DDR5 Memory Specification Rilasciato: Preparare il terreno per DDR5-6400 e oltre

- SK Hynix: Stiamo progettando per DDR5-8400 a 1.1 Volt

- Cadenza DDR5 Aggiornamento: Lancio a 4800 MT/s, Oltre 12 DDR5 Soc in Sviluppo

- Samsung per Produrre DDR5 nel 2021 (con EUV)

- Ecco Alcuni DDR5-4800: Mani-al Primo Sguardo alla Prossima Gen DRAM

- CES 2020: Micron Comincia a Campione DDR5 Rdimm con Partner Server

- SK Hynix Dettagli DDR5-6400

- Keysight Rivela DDR5 Test & Sistema di Validazione

- SK Hynix Sviluppa Primi 16 Gb DDR5-5200 Chip di Memoria, Demo DDR5 RDIMM

- Cadenza & Micron DDR5 Aggiornamento: 16 Gb Chip in pista per il 2019

- Cadenza e Micron Demo DDR5-4400 IMC e memoria, dovuto nel 2019