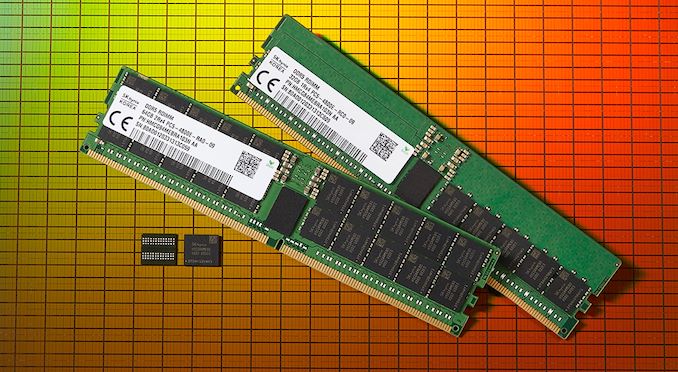

の最初の64GB DDR5-4800モジュールは、メーカーが製品の発売に先立って多種多様なテスト車両を展示しているため、ここ数カ月で次世代 DDR5を使用する予定のプラットフォームも急速に近づいており、徐々に消費者に落ちる前に企業側でのデビューが期待されています。 これらすべてのものと同様に、開発は段階的に行われます:メモリコントローラ、インタフェース、電気的同等のテストIP、およびモジュー SK Hynixが今日発売している最終段階、または少なくともこれらのモジュールに入るチップです。

DDR5は、主要なコンピューティングプラットフォームの大部分で使用するためのプラットフォームメモリの次の段階です。 この仕様(2020年7月にリリース)では、メイン電圧が1.2Vから1.1Vに低下し、最大シリコンダイ密度が4倍に増加し、最大データレートが2倍になり、バースト長が2倍になり、バンクグループ数が2倍になります。 簡単に言えば、JEDEC DDR仕様は、DDR5-6400で動作する128GBのバッファなしモジュールを可能にします。 RDIMMとLrdimmは、はるかに高い電力を可能にする必要があります。

DDRの世界には、仕様に関係するすべての人が反復したい四つの角度があります。 容量は明らかなものですが、メモリ帯域幅は、私たちが見ている大規模なコア数のサーバーで一般的なマルチコアワークロードのパフォーマンススケーリングに 他の2つはパワー(明らかな目標)であり、もう1つはレイテンシ、パフォーマンスのもう1つの重要な指標です。

DDR5では、これを駆動するための主要な変更の一つは、メモリがシステムによって見られる方法です。 DDR5は、モジュールごとに単一の64ビットデータチャネルではなく、モジュールごとに2つの32ビットデータチャネル(またはECCでは40ビット)と見なされます。 つまり、各32ビットチャネルは動作ごとに64バイトを提供しますが、よりインターリーブされた方法でこれを行うことができます。 つまり、標準の”2つの64ビットチャネルDDR4″システムは”クワッド32ビットチャネルDDR5″配置に変形しますが、各メモリスティックは合計64ビットを提供しますが、より制御可能な方法で提供されます。 これにより、ピーク帯域幅を増加させるための重要な要素であるデータレートが2倍になり、より簡単になり、使用中のメモリ上で非同期操作を可能にし、レイテンシを削減するきめの細かいバンクリフレッシュ機能も提供されます。

電圧調整もマザーボードからメモリモジュールに移動され、モジュール自身のニーズを調整することができます。 私たちはすでにDDR4がチップごとのVdroop制御を採用しているのを見ましたが、これは全体のアイデアをより緊密な電力制御と管理のためのさらなる また、マザーボードメーカーではなくモジュールベンダーの手に電源管理を置き、モジュールメーカーがより高速なメモリに必要なものをサイズアップすることができます–間違いなく仕様を上回る非JEDEC標準ゲーミングメモリにどのように異なるファームウェアが対処するかを見ることは興味深いでしょう。

SK Hynixの発表は本日、ddr5ECCメモリのモジュールメーカーへの出荷を開始する準備ができているということです–具体的には、DDR5-4800からDDR5-5600を1.1vでサポー 適切なパッケージング技術(3D TSVなど)を使用すると、sk Hynixはパートナーが256GBのLrdimmを構築できると言います。 よりよいよりjedecの速度のための破片の付加的なbinningはモジュールの製造業者自身によってされなければなりません。 SK Hynixは独自のモジュール、特に32GBと64GBのRdimmをDDR5-4800に搭載しているようで、以前はDDR5-8400までのメモリを提供することを約束していました。

SK Hynixは、これらのモジュールのサブタイミングの情報を提供していません。 JEDEC仕様では、DDR5の三つの異なるモードが定義されています-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B:40-40-40

- DDR5-4800C: 42-42-42

SK Hynixが使用しているこれらのうちのどれが不明です。 モジュールには「4800E」と表示されていますが、JEDEC仕様はDDR5-4800のCL値42を超えていないため、モジュールの命名の一部に過ぎません。帯域幅については、他のメモリメーカーは、DDR5-4800の各モジュールがもたらす理論的な38.4GB/sについて、すでに32GB/sの範囲で有効な数値を見ていると引用し これは、今日DDR4-3200で見ているチャネルあたりの有効な20-25GB/sを超えています。 他のメモリメーカーは、今年の初めから顧客とDDR5をサンプリングしているとすでに発表しています。

発表の一環として、インテルがこれらのモジュールのリードパートナーの一人であることは興味深いものでした。 インテルは、Sapphire Rapids XeonプロセッサプラットフォームでDDR5を有効にすることを約束しており、2021/2022年後半に最初の発売が予定されています。 AMDはこの発表に言及されず、Armのパートナーも言及されなかった。

SK Hynixは、DDR5が2022年に世界市場の10%になると予想され、2024年には43%に増加すると見積もっています。 消費者プラットフォームの交差点は、おそらくDDR4サイクルの半分(または半分以下)に過ぎないため、この時点ではややぼやけています。 従来、市場シェアが等しい場合、古い技術と新しい技術の間のコスト遮断が期待されていましたが、DDR5が必要とする電圧調整の追加コストは、JEDECモジュールの標準的な電力供給からオーバークロックされたモジュールのより強力なソリューションまで、モジュールコストを引き上げる可能性があります。 しかし、その点でマザーボードを安くする必要があります。

出典:SK hynix

関連読書

- DDR5メモリ仕様リリース:Ddr5-6400以降のステージの設定

- SK Hynix:DDR5-8400を1に予定しています。1ボルト

- ケイデンスDDR5アップデート:4800MT/sで発売、開発中の12以上のDDR5Soc

- サムスン、2021年にDDR5を生産(EUV付き)

- ここではいくつかのDDR5-4800があります:次世代DRAM

- CES2020:MicronサーバーパートナーとのサンプルDdr5Rdimm

- Sk hynixの詳細Ddr5-6400

- KeysightがDdr5テストを明らかに&検証システム

- SK Hynixが最初の16gb Ddr5-5200メモリチップ、Ddr5Rdimm

- CADENCE&Micron ddr5アップデート: 2019年に予定されている16Gbチップ

- CadenceおよびMicronのデモDDR5-4400IMCおよびメモリ、2019年に予定されている