VHDLはvery high-speed integrated circuit hardware description languageの略です。 これは、モデリングのデータフロー、行動や構造的なスタイルによってデジタルシステムをモデル化するために使用されるプログ この言語は、VHSICプログラムの下で国防総省(DoD)のために1981年に最初に導入されました。

デザインの記述

vhdlでは、エンティティはハードウェアモジュールを記述するために使用されます。 エンティティは、以下を使用して記述できます,

- エンティティ宣言

- アーキテクチャ

- 構成

- パッケージ宣言

- パッケージ本体

これらが何であるかを見てみましょう。

エンティティ宣言

ハードウェアモジュールの名前、入力出力信号、およびモードを定義します。

−

entity entity_name is Port declaration;end entity_name;

エンティティ宣言は’entity’で始まり、’end’キーワードで終わる必要があります。 方向は入力、出力、またはinoutになります。

| で | ポートを読み取ることができます |

| 出力 | ポートを書き込むことができます |

| Inout | ポートの読み書きが可能 |

| バッファ | ポートは読み書きができ、ソースは一つしか持てません。 |

Architecture−

Architectureは、構造、データフロー、動作、または混合スタイルを使用して記述できます。

−

architecture architecture_name of entity_name architecture_declarative_part;begin Statements;end architecture_name;

ここでは、アーキテクチャ本体を記述するエンティティ名を指定する必要があります。 Architectureステートメントは、’begin’と’énd’キーワードの中にある必要があります。 アーキテクチャ宣言部には、変数、定数、またはコンポーネント宣言を含めることができます。

データフローモデリング

このモデリングスタイルでは、エンティティを通るデータの流れは、並行(並列)信号を使用して表現されます。 VHDLの同時実行文は、WHENおよびGENERATEです。

それらのほかに、演算子のみを使用した割り当て(AND、NOT、+、*、sllなど)。)コードを構築するためにも使用できます。

最後に、ブロックと呼ばれる特別な種類の割り当てもこの種のコードで使用できます。

同時実行コードでは、次のものを使用できます−

- 演算子

- WHENステートメント(WHEN/ELSEまたはWITH/SELECT/WHEN);

- GENERATEステートメント;

- ブロックステートメント

ビヘイビアモデリング

このモデリングスタイルでは、文のセットとしてのエンティティの動作は、指定された順序で連続して実行されます。 プロセス、関数、またはプロシージャー内に配置されたステートメントのみが逐次的です。

プロセス、関数、およびプロシージャは、コードの唯一のセクションであり、順番に実行されます。

しかし、全体として、これらのブロックのいずれも、外部に配置された他の文と並行しています。

動作コードの重要な側面の1つは、シーケンシャルロジックに限定されないということです。 確かに、それを使って、順序回路と組み合わせ回路を構築することができます。

動作ステートメントは、IF、WAIT、CASE、およびLOOPです。 変数も制限されており、順次コードでのみ使用されることになっています。 変数はグローバルにすることはできませんので、その値を直接渡すことはできません。

構造モデリング

このモデリングでは、エンティティは相互接続されたコンポーネントのセットとして記述されます。 コンポーネントのインスタンス化文は、並行文です。 したがって、これらの文の順序は重要ではありません。 モデリングの構造スタイルは、コンポーネント自体の動作やそれらが集合的に表すエンティティの動作を意味することなく、コンポーネントの相互接続(ブラックボックスと見なされる)のみを記述します。

構造モデリングでは、アーキテクチャ本体は、宣言部分(キーワードbeginの前)とステートメント部分(キーワードbeginの後)の二つの部分で構成されています。

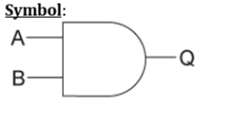

論理演算–ANDゲート

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

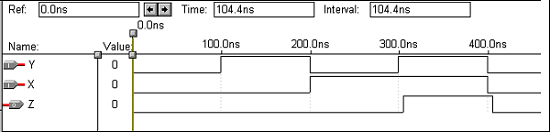

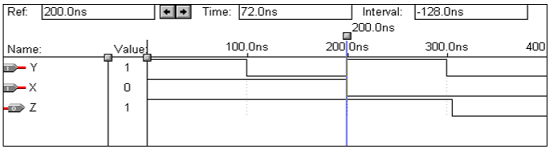

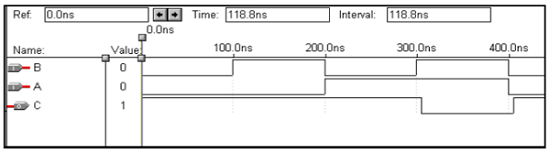

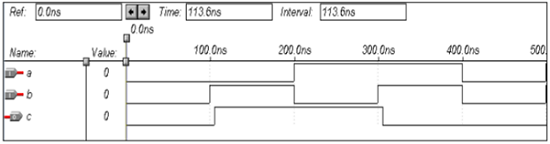

波形

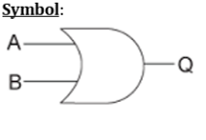

論理演算-ORゲート

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

波形

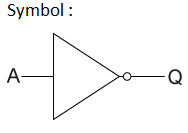

論理演算–NOTゲート

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

波形

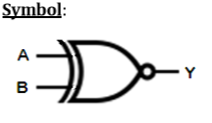

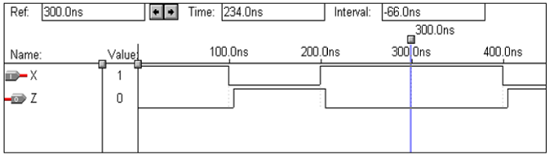

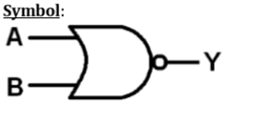

論理演算-NANDゲート

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

波形

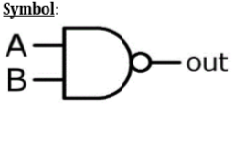

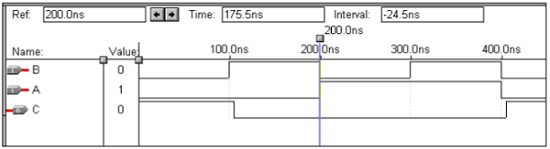

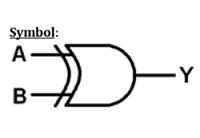

論理演算-NORゲート

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

波形

論理演算-XORゲート

| X | Y | |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

波形

論理演算-X-NORゲート