Diskusjon av neste generasjon DDR-minne har vært aflutter de siste månedene, da produsenter har vist et bredt utvalg av testbiler før en full produktlansering. Plattformer som planlegger Å bruke DDR5 nærmer seg også raskt, med en forventet debut på bedriftssiden før de sakte trickling ned til forbrukeren. Som med alle disse tingene, kommer utviklingen i etapper: minnekontrollere, grensesnitt, elektrisk ekvivalent testing IP OG moduler. DET er det siste stadiet SOM SK Hynix lanserer i dag, eller i det minste sjetongene som går inn i disse modulene.

DDR5 ER neste trinn i plattformminne for bruk i de fleste store databehandlingsplattformer. Spesifikasjonen (som utgitt i juli 2020) bringer hovedspenningen ned fra 1.2 V til 1.1 V, øker maksimal silisiumdensitet med en faktor 4, dobler maksimal datahastighet, dobler burstlengden og dobler antall bankgrupper. Enkelt sagt, JEDEC DDR-spesifikasjonene tillater en 128 GB ubufret modul som kjører PÅ DDR5-6400. RDIMMs og LRDIMMs skal kunne gå mye høyere, kraft tillater det.

DET er fire vinkler i VERDEN AV DDR som alle som er involvert i spesifikasjonen ønsker å iterere på. Kapasitet er den åpenbare, men også minnebåndbredde spiller en nøkkelrolle i ytelsesskalering av vanlige multi-core arbeidsbelastninger i de store core-count serverne vi ser. De to andre er kraft (et åpenbart mål), og den andre er latens, en annen viktig metrisk for ytelse.

MED DDR5, en av de store endringene for å hjelpe kjøre dette er måten minnet er sett av systemet. I stedet for å være en enkelt 64-biters datakanal per modul, ses DDR5 som to 32-biters datakanaler per modul (eller 40 biter I ECC). Bristlengden er doblet, noe som betyr at hver 32-biters kanal fortsatt vil levere 64 byte per operasjon, men kan gjøre det på en mer interleaved måte. Det betyr at standard ‘to 64-bits kanal DDR4’-systemet vil forvandle seg til et ‘quad 32-bits KANAL DDR5’ – arrangement, selv om hver minnepinne gir totalt 64-bits, men på en mer kontrollerbar måte. Dette gjør også dobling av datahastigheten, et nøkkelelement i å øke topp båndbredde, lettere, samt en finere kornet bankoppdateringsfunksjon, som muliggjør asynkrone operasjoner på minnet mens det er i bruk, og reduserer ventetid.

Spenningsregulering flyttes også fra hovedkortet til minnemodulen, slik at modulen kan regulere sine egne behov. VI så ALLEREDE DDR4 vedta en per-chip Vdroop-kontroll, men dette tar hele ideen et skritt videre for strammere strømstyring og styring. Det setter også strømstyring i hendene på modulleverandøren i stedet for hovedkortprodusenten – slik at modulprodusenten kan størrelse opp det som kreves for raskere minne-det vil være interessant å se hvordan forskjellig firmware takler ikke-JEDEC standard spillminne som utvilsomt vil gå over spesifikasjonen.

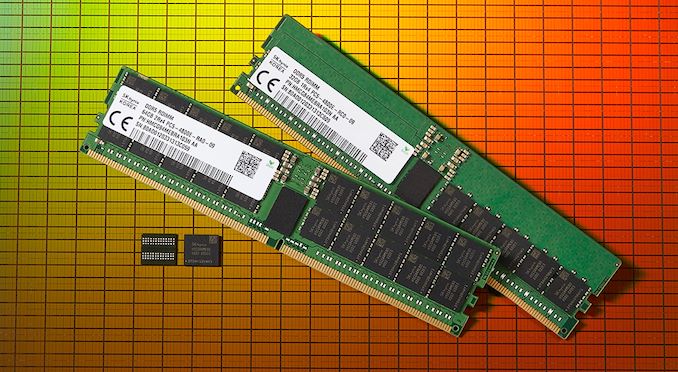

SK Hynix kunngjøring i dag er at de er klare til å begynne å sende ddr5 ECC-minne til modulprodusenter-spesielt 16 gigabit-dør bygget på sin 1ynm-prosess som støtter DDR5 – 4800 TIL DDR5-5600 ved 1.1 volt. MED riktig emballasjeteknologi (FOR EKSEMPEL 3D TSV), SIER SK Hynix at partnere kan bygge 256 GB LRDIMMs. Ytterligere binning av sjetongene for bedre enn JEDEC-hastigheter må gjøres av modulprodusentene selv. SK Hynix ser også ut til å ha egne moduler, spesielt 32GB OG 64gb RDIMMs PÅ DDR5-4800, og har tidligere lovet å tilby minne opp TIL DDR5-8400.

SK Hynix har ikke gitt informasjon om sub-timings av disse modulene. Jedec-spesifikasjonen definerer tre forskjellige moduser FOR DDR5-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B: 40-40-40

- DDR5-4800C: 42-42-42

Det er uklart hvilken AV DISSE SOM SK Hynix bruker. Modulen sier ‘4800E’, men det ser ut til å bare være en del av modulnavnet, da JEDEC-spesifikasjonen ikke går utover EN CL-verdi på 42 FOR DDR5-4800.

for båndbredde har andre minneprodusenter sitert at for den teoretiske 38.4 GB / s som hver modul AV DDR5-4800 kan bringe, ser de allerede effektive tall i 32 GB/s-serien. Dette er over den effektive 20-25 GB / s per kanal som vi ser PÅ DDR4-3200 i dag. Andre minneprodusenter har allerede annonsert AT DE er prøvetaking DDR5 med kunder siden begynnelsen av året.

Som en del av kunngjøringen var Det interessant Å se Intel som en av hovedpartnerne for disse modulene. Intel har forpliktet SEG til å aktivere DDR5 på Sin Sapphire Rapids Xeon-prosessorplattform, på grunn av lansering i slutten av 2021/2022. AMD ble ikke nevnt med kunngjøringen, og Det var heller ikke Noen Arm-partnere.

SK Hynix siterer AT DDR5 forventes å være 10% av det globale markedet i 2022, og øker til 43% i 2024. Krysspunktet for forbrukerplattformer er noe uskarpt på dette punktet, da vi sannsynligvis bare er halvveis gjennom (eller mindre enn halvparten) AV DDR4-syklusen. Tradisjonelt forventer vi en kostnadsavslutning mellom gammel og ny teknologi når de er like i markedsandel, men tilleggskostnadene I spenningsregulering som ddr5 krever, vil trolig øke modulkostnadene-skalering fra standard strømforsyning PÅ JEDEC-moduler opp til en biffere løsning på overklokkede moduler. Det bør imidlertid gjøre hovedkort billigere i den forbindelse.

Kilde: SK hynix

Relatert Lesing

- Ddr5-Minnespesifikasjon Utgitt: Sette Scenen FOR DDR5-6400 og Utover

- SK Hynix: Vi Planlegger FOR DDR5-8400 på 1.1 Volt

- Cadence DDR5 Oppdatering: Lansering på 4800 MT/s, Over 12 Ddr5 SoCs I Utvikling

- Samsung Å Produsere DDR5 i 2021 (MED EUV)

- Her ER NOEN DDR5-4800: Hands-On Første Titt På Neste Gen DRAM

- CES 2020: Micron Begynner Å eksempel Ddr5 Rdimms Med Server Partnere

- sk hynix DETALJER ddr5-6400

- Keysight Avslører Ddr5 Testing & valideringssystem

- sk hynix Utvikler første 16 GB Ddr5-5200 Minnebrikke, Demoer Ddr5 RDIMM

- tråkkfrekvens & micron Ddr5 Oppdatering: 16 Gb Chips på Sporet for 2019

- Kadens Og Micron Demo Ddr5 – 4400 IMC OG Minne, Forfaller i 2019