VHDL står for svært høyhastighets integrert krets maskinvare beskrivelse språk. Det er et programmeringsspråk som brukes til å modellere et digitalt system ved dataflyt, atferdsmessig og strukturell modelleringsstil. Dette språket ble først introdusert i 1981 For forsvarsdepartementet (DoD) under VHSIC-programmet.

Beskrive Et Design

i VHDL brukes en enhet til å beskrive en maskinvaremodul. En enhet kan beskrives ved hjelp av,

- Enhetserklæring

- Arkitektur

- Konfigurasjon

- Pakkedeklarasjon

- pakkelegeme

La oss se hva er disse?

Enhetserklæring

den definerer navnene, inngangssignalene og modusene til en maskinvaremodul.

Syntaks−

entity entity_name is Port declaration;end entity_name;

en enhetserklæring bør starte med ‘entity’ og avslutte med’ end ‘ søkeord. Retningen vil være inngang, utgang eller inout.

| I | Port kan leses |

| Ut | Port kan skrives |

| Inout | Port kan leses og skrives |

| Buffer | Port kan leses og skrives, den kan bare ha en kilde. |

Arkitektur –

Arkitektur kan beskrives ved hjelp av strukturell, dataflyt, atferdsmessig eller blandet stil.

Syntaks−

architecture architecture_name of entity_name architecture_declarative_part;begin Statements;end architecture_name;

Her bør vi spesifisere enhetens navn som vi skriver arkitekturlegemet for. Arkitekturerklæringene skal være innenfor søkeordet’ begin ‘og’ é’. Arkitektur deklarativ del kan inneholde variabler, konstanter eller komponentdeklarasjon.

Dataflytmodellering

i denne modelleringsstilen uttrykkes dataflyten gjennom enheten ved hjelp av samtidig (parallelt) signal. De samtidige uttalelsene I VHDL er NÅR og GENERERER.

foruten dem, oppdrag som bare bruker operatører(JA, IKKE, & pluss;,*, sll, etc.) kan også brukes til å konstruere kode.

Endelig kan en spesiell type oppdrag, KALT BLOKK, også brukes i denne typen kode.

i samtidig kode kan følgende brukes−

- Operatorer

- NÅR-setningen (NÅR/ANNET eller MED/VELG/NÅR);

- GENERER-setningen;

- BLOKK-setningen

Atferdsmodellering

i denne modelleringsstilen utføres virkemåten til en enhet som sett med setninger sekvensielt i den angitte rekkefølgen. Bare setninger plassert i EN PROSESS, FUNKSJON ELLER PROSEDYRE er sekvensielle.

PROSESSER, FUNKSJONER og PROSEDYRER er DE eneste delene av koden som utføres sekvensielt.

men som helhet er noen av disse blokkene fortsatt samtidig med andre uttalelser plassert utenfor den.

et viktig aspekt ved adferdskode er at den ikke er begrenset til sekvensiell logikk. Faktisk, med det, kan vi bygge sekvensielle kretser samt kombinasjonskretser.

virkemåten er HVIS, VENT, CASE og LOOP. VARIABLER er også begrenset, og de skal bare brukes i sekvensiell kode. VARIABEL KAN aldri være global, så verdien kan ikke sendes ut direkte.

Strukturell Modellering

i denne modelleringen beskrives en enhet som et sett med sammenkoblede komponenter. En komponent instantiation setning er en samtidig setning. Derfor er rekkefølgen av disse uttalelsene ikke viktig. Den strukturelle stilen til modellering beskriver bare en sammenkobling av komponenter (sett på som svarte bokser), uten å antyde noen oppførsel av komponentene selv eller av enheten som de kollektivt representerer.

i Strukturell modellering består arkitekturlegemet av to deler – den deklarative delen (før søkeordet begynner) og setningsdelen(etter at søkeordet begynner).

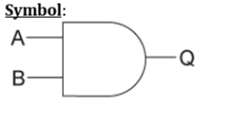

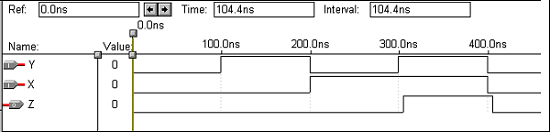

Logisk Operasjon – OG PORT

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

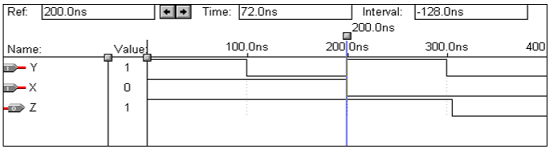

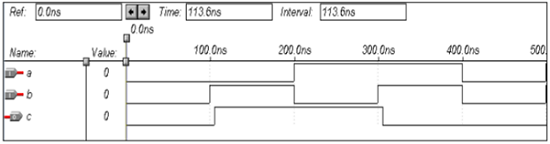

Bølgeformer

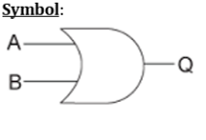

Logisk Operasjon – Eller Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Bølgeformer

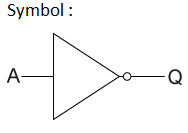

Logisk Operasjon – IKKE Gate

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

Bølgeformer

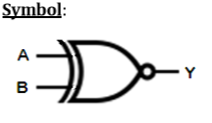

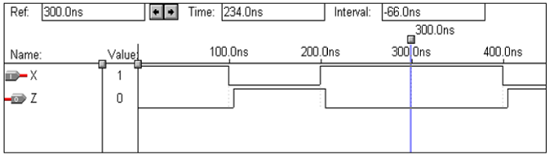

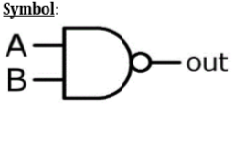

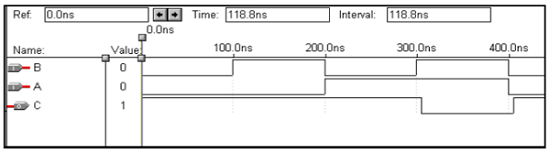

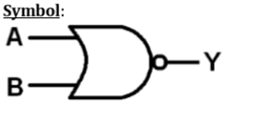

Logisk Operasjon – Nand Gate

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Bølgeformer

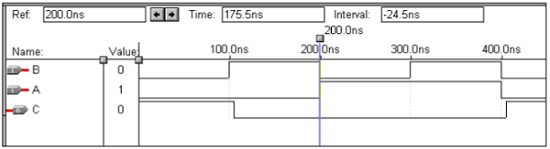

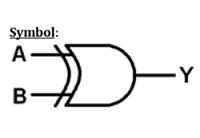

Logisk Operasjon – Nor Gate

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Bølgeformer

Logisk Operasjon – Xor Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Bølgeformer

Logisk Operasjon-X-Nor Gate