dyskusja na temat nowej generacji pamięci DDR była w ostatnich miesiącach burzliwa, ponieważ producenci prezentowali szeroką gamę pojazdów testowych przed pełną premierą produktu. Platformy, które planują używać DDR5, również szybko się zbliżają, z oczekiwanym debiutem po stronie przedsiębiorstwa, zanim powoli spadnie do konsumenta. Podobnie jak w przypadku wszystkich tych rzeczy, rozwój odbywa się etapami: kontrolery pamięci, interfejsy, elektryczne równoważne testowanie IP i moduły. To ostatni etap, który SK Hynix uruchamia dzisiaj, a przynajmniej chipy, które wchodzą do tych modułów.

DDR5 jest kolejnym etapem pamięci platformowej do użytku w większości głównych platform obliczeniowych. Specyfikacja (wydana w lipcu 2020 r.) obniża główne napięcie z 1,2 V do 1,1 V, zwiększa maksymalną gęstość matrycy krzemu o współczynnik 4, podwaja maksymalną szybkość transmisji danych, podwaja długość serii i podwaja liczbę grup bankowych. Mówiąc najprościej, Specyfikacja JEDEC DDR pozwala na 128 GB niebuforowanego modułu pracującego w pamięci DDR5-6400. Rdimmy i Lrdimmy powinny być w stanie pójść znacznie wyżej, jeśli pozwoli na to moc.

w świecie DDR istnieją cztery kąty, na których każdy zaangażowany w specyfikację chce iterować. Pojemność jest oczywista, ale także przepustowość pamięci odgrywa kluczową rolę w skalowaniu wydajności typowych wielordzeniowych obciążeń w dużych serwerach z liczbą rdzeni, które obserwujemy. Pozostałe dwa to moc (oczywisty cel), a drugi to opóźnienie, kolejny kluczowy wskaźnik wydajności.

w przypadku pamięci DDR5 jedną z głównych zmian, które mają pomóc w napędzie, jest sposób, w jaki pamięć jest postrzegana przez system. Zamiast być pojedynczym 64-bitowym kanałem danych na moduł, DDR5 jest postrzegany jako dwa 32-bitowe kanały danych na moduł (lub 40 bitów w ECC). Długość serii podwoiła się, co oznacza, że każdy 32-bitowy kanał nadal będzie dostarczał 64 bajty na operację, ale może to zrobić w bardziej przeplatany sposób. Oznacza to, że standardowy system „dwóch 64-bitowych kanałów DDR4” przekształci się w układ „quad 32-bitowych kanałów DDR5”, chociaż każda pamięć Memory stick zapewnia łącznie 64-bitowe, ale w bardziej kontrolowany sposób. Ułatwia to również podwojenie szybkości transmisji danych, kluczowego elementu zwiększającego szczytową przepustowość, a także drobniejszą funkcję odświeżania banku, która pozwala na asynchroniczne operacje na pamięci podczas jej użytkowania, zmniejszając opóźnienia.

regulacja napięcia jest również przenoszona z płyty głównej do modułu pamięci, umożliwiając modułowi regulację własnych potrzeb. Widzieliśmy już, jak DDR4 przyjmuje sterowanie vdroop na układ scalony, ale to zajmuje cały pomysł o krok dalej w celu ściślejszej kontroli mocy i zarządzania nią. To również stawia zarządzanie energią w rękach producenta modułu, a nie producenta płyty głównej, pozwalając producentowi modułu na rozmiar tego, co jest wymagane do szybszej pamięci – interesujące będzie zobaczyć, jak różne oprogramowanie radzi sobie ze standardową pamięcią Gamingową, która bez wątpienia przekroczy specyfikację.

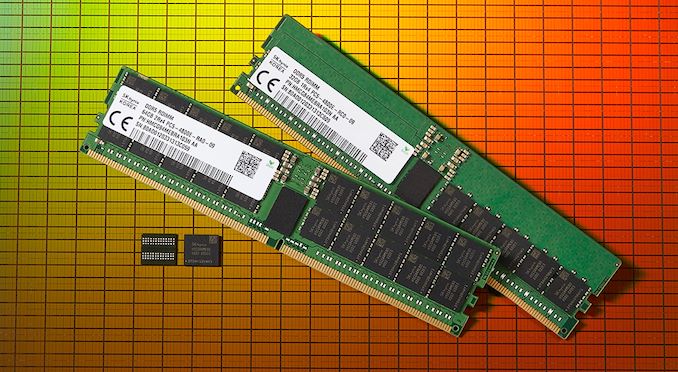

firma SK Hynix ogłosiła dziś, że jest gotowa do rozpoczęcia wysyłki pamięci DDR5 ECC do producentów modułów – w szczególności 16 gigabitowych matryc zbudowanych w procesie 1Ynm, które obsługują DDR5-4800 do DDR5-5600 przy napięciu 1,1 V. Dzięki odpowiedniej technologii pakowania (takiej jak 3D TSV), SK Hynix mówi, że partnerzy mogą zbudować 256 GB LRDIMMs. Dodatkowe binning chipów dla lepszej prędkości niż JEDEC będą musieli zrobić sami producenci modułów. SK Hynix wydaje się również mieć własne moduły, w szczególności 32GB i 64GB RDIMMs w DDR5-4800, i wcześniej obiecał zaoferować pamięci do DDR5-8400.

SK Hynix nie dostarczył informacji o podokresach tych modułów. Specyfikacja JEDEC definiuje trzy różne tryby dla DDR5-4800:

- DDR5-4800A: 34-34-34

- DDR5 – 4800B: 40-40-40

- DDR5-4800C: 42-42-42

nie jest jasne, którego z nich używa SK Hynix. Moduł mówi „4800E”, jednak wydaje się to być tylko częścią nazwy modułu, ponieważ specyfikacja JEDEC nie wykracza poza wartość CL 42 dla DDR5-4800.

w odniesieniu do przepustowości, inni producenci pamięci podali, że dla teoretycznej 38,4 GB/s, jaką może przynieść każdy moduł DDR5-4800, już widzą efektywne liczby w zakresie 32 GB/s. Jest to powyżej efektywnych 20-25 GB / s na Kanał, które widzimy dzisiaj na DDR4 – 3200. Inni producenci pamięci już zapowiedzieli, że od początku roku próbkują DDR5 z klientami.

w ramach Zapowiedzi interesujące było, że Intel jest jednym z głównych partnerów tych modułów. Intel zobowiązał się do włączenia pamięci DDR5 na platformie procesorowej Sapphire Rapids Xeon, która ma zostać wprowadzona na rynek na przełomie 2021/2022. Firma AMD nie została wymieniona w ogłoszeniu, podobnie jak żaden z partnerów Arm.

SK Hynix cytuje, że oczekuje się, że DDR5 wyniesie 10% światowego rynku w 2022 r., a w 2024 r. wzrośnie do 43%. Punkt przecięcia dla platform konsumenckich jest w tym momencie nieco rozmyty, ponieważ prawdopodobnie jesteśmy tylko w połowie (lub mniej niż w połowie) cyklu DDR4. Tradycyjnie spodziewamy się przechwytywania kosztów między starą i nową technologią, gdy mają one równy udział w rynku, jednak dodatkowe koszty regulacji napięcia, które wymagają pamięci DDR5, prawdopodobnie zwiększą koszty modułów-od standardowego zasilania modułów JEDEC po lepsze rozwiązanie dla przetaktowanych modułów. Powinno to jednak sprawić, że Płyty główne będą tańsze pod tym względem.

źródło: SK hynix

powiązany odczyt

- Specyfikacja pamięci DDR5: ustawienie etapu dla DDR5-6400 i więcej

- SK Hynix: planujemy dla DDR5-8400 na 1.1 V

- aktualizacja DDR5 Cadence: uruchomienie z prędkością 4800 MT/s, ponad 12 układów Soc DDR5 w fazie rozwoju

- Samsung wyprodukuje DDR5 w 2021 roku (z EUV)

- oto kilka DDR5-4800: pierwsze spojrzenie na pamięć DRAM następnej generacji

- CES 2020: Micron zaczyna aby przetestować pamięć DDR5 RDIMMs z partnerami serwerów

- SK Hynix szczegóły DDR5-6400

- Keysight ujawnia testowanie pamięci DDR5 & system walidacji

- SK Hynix opracowuje pierwszy układ pamięci DDR5-5200 o pojemności 16 GB, dema DDR5 RDIMM

- Cadence & Micron aktualizacja DDR5: 16 GB chipów na torze dla 2019

- Cadence i Micron Demo DDR5-4400 IMC i pamięci, Due in 2019