diskussionen om nästa generation av DDR-minne har varit aflutter under de senaste månaderna som tillverkare har visat upp ett brett utbud av testfordon inför en fullständig produktlansering. Plattformar som planerar att använda DDR5 närmar sig också snabbt, med en förväntad debut på företagssidan innan de långsamt sipprar ner till konsumenten. Som med alla dessa saker kommer utvecklingen i steg: minneskontroller, gränssnitt, elektrisk ekvivalent testning IP och moduler. Det är det sista steget som SK Hynix lanserar idag, eller åtminstone de chips som går in i dessa moduler.

DDR5 är nästa steg i plattformsminnet för användning i de flesta större beräkningsplattformar. Specifikationen (som släpptes i juli 2020) sänker huvudspänningen från 1,2 V till 1,1 V, ökar den maximala kiseldysdensiteten med en faktor 4, fördubblar den maximala datahastigheten, fördubblar spränglängden och fördubblar antalet bankgrupper. Enkelt uttryckt tillåter JEDEC DDR-specifikationerna en 128 GB obuffrad modul som körs på DDR5-6400. RDIMM och LRDIMM bör kunna gå mycket högre, kraft tillåter.

det finns fyra vinklar i DDR-världen som alla som är involverade i specifikationen vill iterera på. Kapaciteten är den uppenbara, men även minnesbandbredd spelar en nyckelroll i prestandaskalning av vanliga arbetsbelastningar med flera kärnor i de stora kärnantalsservrarna vi ser. De andra två är makt (ett uppenbart mål), och den andra är latens, en annan viktig metrisk för prestanda.

med DDR5, en av de stora förändringarna för att hjälpa till att köra detta är hur minnet ses av systemet. I stället för att vara en enda 64-bitars datakanal per modul ses DDR5 som två 32-bitars datakanaler per modul (eller 40 bitar i ECC). Burstlängden har fördubblats, vilket innebär att varje 32-bitars kanal fortfarande kommer att leverera 64 byte per operation, men kan göra det på ett mer interfolierat sätt. Det betyder att standard ’två 64-bitars kanal DDR4′ – systemet kommer att förvandlas till ett’ quad 32-bitars kanal DDR5 ’ -arrangemang, även om varje minne ger totalt 64-bitar men på ett mer kontrollerbart sätt. Detta gör också fördubbling av datahastigheten, ett nyckelelement för att öka toppbandbredden, lättare, liksom en finkornig bankuppdateringsfunktion, vilket möjliggör asynkrona operationer på minnet medan det används, vilket minskar latensen.

spänningsreglering flyttas också från moderkortet till minnesmodulen, vilket gör att modulen kan reglera sina egna behov. Vi såg redan DDR4 anta en per-chip Vdroop-kontroll, men det tar hela tanken ett steg längre för strängare kraftstyrning och hantering. Det sätter också strömhantering i händerna på modulleverantören snarare än moderkortstillverkaren, vilket gör att modultillverkaren kan storlek upp vad som krävs för snabbare minne – det blir intressant att se hur olika firmware klarar av icke-JEDEC-standardspelminne som utan tvekan kommer att gå över specifikationen.

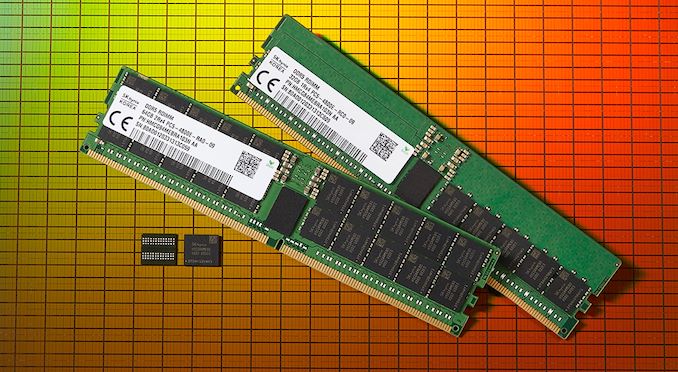

SK Hynix tillkännagivande idag är att de är redo att börja leverera DDR5 ECC – minne till modultillverkare-specifikt 16 gigabit dör byggda på sin 1ynm-process som stöder DDR5-4800 till DDR5-5600 vid 1.1 volt. Med rätt förpackningsteknik (som 3D TSV) säger SK Hynix att partners kan bygga 256 GB LRDIMM. Ytterligare binning av chipsen för bättre än JEDEC-hastigheter måste göras av modultillverkarna själva. SK Hynix verkar också ha sina egna moduler, specifikt 32 GB och 64 GB RDIMM på DDR5-4800, och har tidigare lovat att erbjuda minne upp till DDR5-8400.

SK Hynix har inte lämnat information om deltiderna för dessa moduler. JEDEC-specifikationen definierar tre olika lägen för DDR5-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B: 40-40-40

- DDR5-4800C: 42-42-42

det är oklart vilken av dessa som SK Hynix använder. Modulen säger ’4800E’, men det verkar bara vara en del av modulnamnet, eftersom JEDEC-specifikationen inte går utöver ett CL-värde på 42 för DDR5-4800.

för bandbredd har andra minnestillverkare citerat att för de teoretiska 38, 4 GB/s som varje modul i DDR5-4800 kan ge, ser de redan effektiva siffror i 32 GB/s-området. Detta är över den effektiva 20-25 GB/s per kanal som vi ser på DDR4-3200 idag. Andra minnestillverkare har redan meddelat att de samplar DDR5 med kunder sedan början av året.

som en del av tillkännagivandet var det intressant att se Intel som en av huvudpartnerna för dessa moduler. Intel har åtagit sig att möjliggöra DDR5 på sin Sapphire Rapids Xeon-processorplattform, på grund av den första lanseringen i slutet av 2021/2022. AMD nämndes inte med tillkännagivandet, och inte heller var några Arm-partners.

SK Hynix citerar att DDR5 förväntas vara 10% av den globala marknaden 2022 och öka till 43% 2024. Skärningspunkten för konsumentplattformar är något suddig vid denna tidpunkt, eftersom vi förmodligen bara är halvvägs (eller mindre än hälften) av DDR4-cykeln. Traditionellt förväntar vi oss en kostnadsavlyssning mellan Gammal och ny teknik när de är lika i marknadsandel, men de extra kostnaderna i spänningsreglering som DDR5 kräver kommer sannolikt att driva upp modulkostnader – skalning från standardströmleverans på JEDEC-moduler upp till en biffigare lösning på de överklockade modulerna. Det bör dock göra moderkort billigare i det avseendet.

källa: SK hynix

relaterad läsning

- DDR5-Minnesspecifikation släppt: ställa in scenen för DDR5-6400 och därefter

- SK Hynix: vi planerar för DDR5-8400 vid 1.1 volt

- Cadence DDR5-uppdatering: startar vid 4800 MT/s, över 12 DDR5 SoCs under utveckling

- Samsung för att producera DDR5 2021 (med EUV)

- här är några DDR5-4800: Hands-On första titt på Nästa Gen DRAM

- CES 2020: Micron börjar prov DDR5 RDIMM med Serverpartners

- SK Hynix detaljer DDR5-6400

- Keysight avslöjar DDR5 testning & valideringssystem

- SK Hynix utvecklar första 16 GB DDR5-5200 minneskrets, demos DDR5 RDIMM

- kadens & micron DDR5 Uppdatering: 16 Gb Chips på rätt spår för 2019

- kadens och Micron Demo DDR5 – 4400 IMC och minne, på grund av 2019