VHDL står för very high-speed integrated circuit hardware description language. Det är ett programmeringsspråk som används för att modellera ett digitalt system genom dataflöde, beteendemässig och strukturell modelleringsstil. Detta språk introducerades först 1981 för försvarsdepartementet (DoD) under vhsic-programmet.

beskriva en Design

i VHDL används en enhet för att beskriva en hårdvarumodul. En enhet kan beskrivas med,

- Entitetsdeklaration

- arkitektur

- konfiguration

- paketdeklaration

- Paketkropp

Låt oss se vad är dessa?

Entity Declaration

den definierar namn, ingångssignaler och lägen för en hårdvarumodul.

Syntax−

entity entity_name is Port declaration;end entity_name;

en entitetsdeklaration bör börja med’ entity ’och sluta med’ end ’ nyckelord. Riktningen kommer att matas in, matas ut eller inout.

| i | Port kan läsas |

| ut | Port kan skrivas |

| Inout | Port kan läsas och skrivas |

| buffert | Port kan läsas och skrivas, den kan bara ha en källa. |

arkitektur –

arkitektur kan beskrivas med strukturell, dataflöde, beteende eller blandad stil.

Syntax−

architecture architecture_name of entity_name architecture_declarative_part;begin Statements;end architecture_name;

här bör vi ange enhetens namn för vilket vi skriver arkitekturkroppen. Arkitekturuttalandena ska vara inne i nyckelordet’ begin ’och’ exceptional’. Arkitekturdeklarativ del kan innehålla variabler, konstanter eller komponentdeklaration.

Dataflödesmodellering

i denna modelleringsstil uttrycks flödet av data genom enheten med samtidig (parallell) signal. De samtidiga uttalandena i VHDL är när och genererar.

förutom dem, uppdrag med endast operatörer(och, inte, & plus;,*, sll, etc.) kan också användas för att konstruera kod.

slutligen kan en speciell typ av uppdrag, kallad BLOCK, också användas i denna typ av kod.

i samtidig kod kan följande användas−

- operatorer

- when-satsen (när / annars eller med / SELECT / WHEN);

- GENERATE-satsen;

- BLOCK-satsen

Behavioral Modeling

i denna modelleringsstil exekveras beteendet hos en entitet som uppsättning uttalanden sekventiellt i den angivna ordningen. Endast uttalanden placerade i en PROCESS, funktion eller procedur är sekventiella.

processer, funktioner och procedurer är de enda avsnitten av kod som exekveras sekventiellt.

men som helhet är något av dessa block fortfarande samtidigt med andra uttalanden som placeras utanför den.

en viktig aspekt av beteendekoden är att den inte är begränsad till sekventiell logik. Med det kan vi faktiskt bygga sekventiella kretsar såväl som kombinationskretsar.

beteendeuttalandena är IF, WAIT, CASE och LOOP. Variabler är också begränsade och de ska endast användas i sekventiell kod. Variabel kan aldrig vara global, så dess värde kan inte skickas ut direkt.

strukturell modellering

i denna modellering beskrivs en enhet som en uppsättning sammankopplade komponenter. En komponent instansiering uttalande är en samtidig uttalande. Därför är ordningen för dessa uttalanden inte viktig. Den strukturella stilen för modellering beskriver endast en sammankoppling av komponenter (ses som svarta lådor), utan att antyda något beteende hos komponenterna själva eller av den enhet som de kollektivt representerar.

i Strukturmodellering består arkitekturkroppen av två delar − den deklarativa delen (innan nyckelordet börjar) och uttalande delen (efter nyckelordet börjar).

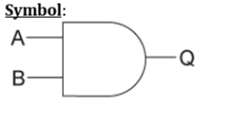

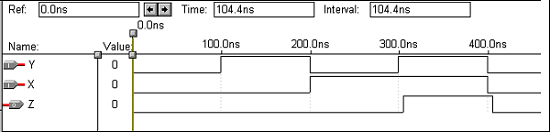

Logic Operation – och GATE

| X | y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

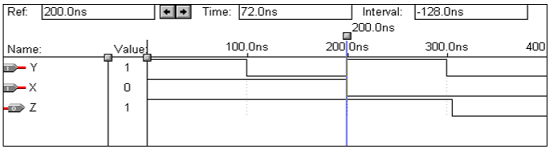

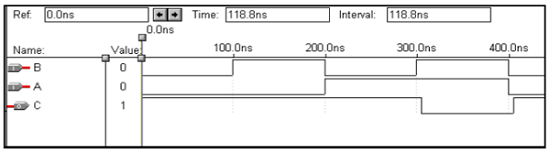

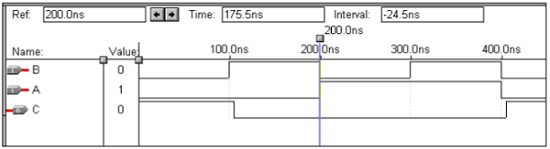

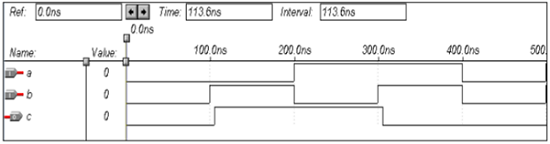

vågformer

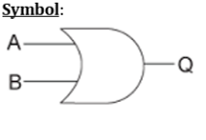

Logic Operation – eller Gate

| X | y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

vågformer

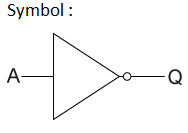

logisk Drift – inte Grind

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

vågformer

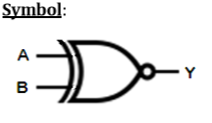

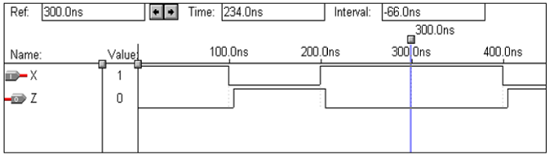

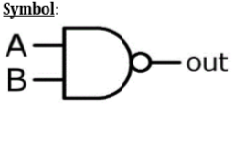

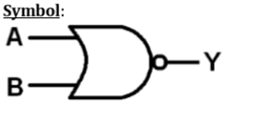

logisk Drift – NAND Gate

| X | y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

vågformer

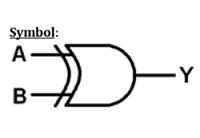

logisk Drift – Nor Gate

| X | y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

vågformer

logisk Drift – xor Gate

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

vågformer

logisk Drift-X – Nor Gate