diskussion af den næste generation af DDR-hukommelse har været aflutter i de seneste måneder, da producenterne har fremvist en bred vifte af testkøretøjer forud for en fuld produktlancering. Platforme, der planlægger at bruge DDR5, nærmer sig også hurtigt, med en forventet debut på virksomhedssiden, før de langsomt siver ned til forbrugeren. Som med alle disse ting kommer udviklingen i etaper: hukommelsescontrollere, grænseflader, elektrisk ækvivalent test IP og moduler. Det er den sidste fase, som SK Hyniks lancerer i dag, eller i det mindste de chips, der går ind i disse moduler.

DDR5 er den næste fase af platformhukommelsen til brug i de fleste større beregningsplatforme. Specifikationen (som frigivet i juli 2020) bringer hovedspændingen ned fra 1,2 V til 1,1 V, øger den maksimale siliciumdysetæthed med en faktor 4, fordobler den maksimale datahastighed, fordobler burstlængden og fordobler antallet af bankgrupper. Kort sagt giver JEDEC DDR-specifikationerne mulighed for et 128 GB unbuffered modul, der kører på DDR5-6400. RDIMMs og LRDIMMs bør være i stand til at gå meget højere, magt tillader.

der er fire vinkler i DDR ‘ s verden, som alle involverede i specifikationen ønsker at gentage. Kapacitet er den åbenlyse, men også hukommelsesbåndbredde spiller en nøglerolle i ydelsesskalering af almindelige multi-core-arbejdsbelastninger i de store core-count-servere, vi ser. De to andre er magt (et indlysende mål), og den anden er latenstid, en anden nøglemetrik for ydeevne.

med DDR5 er en af de store ændringer, der hjælper med at drive dette, den måde, hukommelsen ses af systemet. I stedet for at være en enkelt 64-bit datakanal pr.modul ses DDR5 som to 32-bit datakanaler pr. modul (eller 40 bit i ECC). Burstlængden er fordoblet, hvilket betyder, at hver 32-bit kanal stadig vil levere 64 bytes pr. Det betyder, at standard ‘to 64-bit kanal DDR4′ – systemet vil blive omdannet til et’ firhjuls 32-bit kanal DDR5 ‘ arrangement, selvom hver memory stick giver i alt 64-bit, men på en mere kontrollerbar måde. Dette gør også fordobling af datahastigheden, et nøgleelement i stigende spidsbåndbredde, lettere såvel som en finere kornet bankopdateringsfunktion, som giver mulighed for asynkrone operationer på hukommelsen, mens den er i brug, hvilket reducerer latenstid.

spændingsregulering flyttes også fra bundkortet til hukommelsesmodulet, så modulet kan regulere sine egne behov. Vi så allerede DDR4 vedtage en per-chip Vdroop-kontrol, men dette tager hele ideen et trin videre for strammere strømstyring og styring. Det lægger også strømstyring i hænderne på modulleverandøren snarere end bundkortproducenten, så modulproducenten kan dimensionere det, der kræves for hurtigere hukommelse – det vil være interessant at se, hvordan forskellige firmaer håndterer ikke-JEDEC standard gaming-hukommelse, der uden tvivl vil gå over specifikationen.

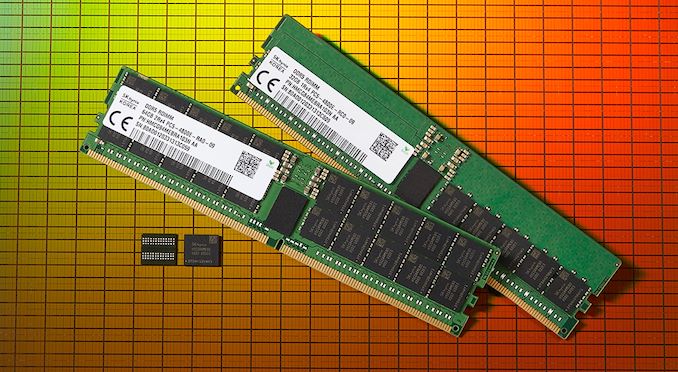

SK Hyniks meddelelse i dag er, at de er klar til at begynde at sende DDR5 ECC – hukommelse til modulproducenter-specifikt 16 gigabit-dør bygget på sin 1ynm-proces, der understøtter DDR5-4800 til DDR5-5600 ved 1, 1 volt. 3D TSV), siger SK Hyniks, at partnere kan bygge 256 GB LRDIMMs. Yderligere binning af chips til bedre end JEDEC-hastigheder skal udføres af modulproducenterne selv. SK ser også ud til at have sine egne moduler, specifikt 32 GB og 64 GB RDIMMs ved DDR5-4800, og har tidligere lovet at tilbyde hukommelse op til DDR5-8400.

SK har ikke givet oplysninger om undertiderne for disse moduler. JEDEC-specifikationen definerer tre forskellige tilstande til DDR5-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B: 40-40-40

- DDR5-4800C: 42-42-42

det er uklart, hvilken af disse SK Hyniks bruger. Modulet siger ‘4800e’, men det ser ud til at være en del af modulnavnet, da JEDEC-specifikationen ikke går ud over en CL-værdi på 42 for DDR5-4800.

for båndbredde har andre hukommelsesproducenter Citeret, at for de teoretiske 38, 4 GB/s, som hvert modul i DDR5-4800 kan bringe, ser de allerede effektive tal i 32 GB/s-området. Dette er over den effektive 20-25 GB/s pr kanal, som vi ser på DDR4-3200 i dag. Andre hukommelsesproducenter har allerede meddelt, at de prøver DDR5 med kunder siden begyndelsen af året.

som en del af meddelelsen var det interessant at se Intel som en af de førende partnere for disse moduler. Intel har forpligtet sig til at aktivere DDR5 på sin Sapphire Rapids-processorplatform, der skal lanceres i slutningen af 2021/2022. AMD blev ikke nævnt med meddelelsen, og heller ikke nogen Arm-partnere.

SK siger, at DDR5 forventes at være 10% af det globale marked i 2022 og stige til 43% i 2024. Skæringspunktet for forbrugerplatforme er noget sløret på dette tidspunkt, da vi sandsynligvis kun er halvvejs igennem (eller mindre end halvdelen) af DDR4-cyklussen. Traditionelt forventer vi en omkostningsaflytning mellem gammel og ny teknologi, når de er ens i markedsandel, men de ekstra omkostninger i spændingsregulering, som DDR5 kræver, vil sandsynligvis øge modulomkostningerne – skalering fra standard strømforsyning på JEDEC-moduler op til en bedre løsning på de overclocked moduler. Det bør dog gøre bundkort billigere i den henseende.

kilde: SK hyniks

relateret læsning

- DDR5 Hukommelsesspecifikation frigivet: Indstilling af scenen for DDR5-6400 og videre

- SK Hyniks: vi planlægger DDR5-8400 på 1.1 Volt

- Cadence DDR5-opdatering: lancering ved 4800 MT/s, Over 12 DDR5 SOC ‘ er under udvikling

- Samsung producerer DDR5 i 2021 (med EUV)

- her er nogle DDR5-4800: Hands-On første kig på Næste Gen DRAM

- CES 2020: Micron begynder at prøve DDR5 Rdimms med Serverpartnere

- sk hyniks detaljer DDR5-6400

- Keysight afslører DDR5 test & valideringssystem

- sk hyniks Udvikler første 16 GB DDR5-5200 hukommelseschip, demoer DDR5 RDIMM

- kadence & Micron DDR5 opdatering: 16 Gb Chips på sporet for 2019

- kadence og Micron Demo DDR5 – 4400 IMC og hukommelse, forfalder i 2019