El debate sobre la próxima generación de memoria DDR ha sido más intenso en los últimos meses, ya que los fabricantes han estado exhibiendo una amplia variedad de vehículos de prueba antes del lanzamiento completo del producto. Las plataformas que planean usar DDR5 también se están acercando rápidamente, con un debut esperado en el lado empresarial antes de llegar lentamente al consumidor. Al igual que con todas estas cosas, el desarrollo viene en etapas: controladores de memoria, interfaces, IP de prueba equivalente eléctrica y módulos. Es la etapa final que SK Hynix está lanzando hoy, o al menos los chips que van en estos módulos.

DDR5 es la siguiente etapa de la memoria de plataforma para su uso en la mayoría de las principales plataformas informáticas. La especificación (publicada en julio de 2020) reduce el voltaje principal de 1,2 V a 1,1 V, aumenta la densidad máxima de la matriz de silicio en un factor 4, duplica la velocidad máxima de datos, duplica la longitud de ráfaga y duplica el número de grupos de bancos. En pocas palabras, las especificaciones DDR de JEDEC permiten un módulo sin búfer de 128 GB que se ejecuta en DDR5-6400. Los RDIMM y LRDIMM deben poder ir mucho más altos, si la potencia lo permite.

Hay cuatro ángulos en el mundo de DDR que todos los involucrados en la especificación quieren iterar. La capacidad es la obvia, pero también el ancho de banda de memoria juega un papel clave en el escalado del rendimiento de las cargas de trabajo multinúcleo comunes en los servidores de gran cantidad de núcleos que estamos viendo. Los otros dos son la potencia (un objetivo obvio), y el otro es la latencia, otra métrica clave para el rendimiento.

Con DDR5, uno de los principales cambios para ayudar a manejar esto es la forma en que el sistema ve la memoria. En lugar de ser un único canal de datos de 64 bits por módulo, DDR5 se ve como dos canales de datos de 32 bits por módulo (o 40 bits en ECC). La longitud de ráfaga se ha duplicado, lo que significa que cada canal de 32 bits aún entregará 64 bytes por operación, pero puede hacerlo de una manera más intercalada. Eso significa que el sistema estándar ‘dos canales DDR4 de 64 bits’ se transformará en una disposición ‘cuádruple de canales DDR5 de 32 bits’, aunque cada memory stick proporciona un total de 64 bits, pero de una manera más controlable. Esto también facilita la duplicación de la velocidad de datos, un elemento clave para aumentar el ancho de banda máximo, así como una función de actualización de banco de grano más fino, que permite operaciones asíncronas en la memoria mientras está en uso, lo que reduce la latencia.

La regulación de voltaje también se mueve de la placa base al módulo de memoria, lo que permite que el módulo regule sus propias necesidades. Ya vimos que DDR4 adoptaba un control Vdroop por chip, pero esto lleva toda la idea un paso más allá para un control y una gestión de potencia más estrictos. También pone la administración de energía en manos del proveedor del módulo en lugar del fabricante de la placa base, lo que permite al fabricante del módulo dimensionar lo que se requiere para una memoria más rápida: será interesante ver cómo los diferentes firmware hacen frente a la memoria para juegos estándar que no es JEDEC, que sin duda superará las especificaciones.

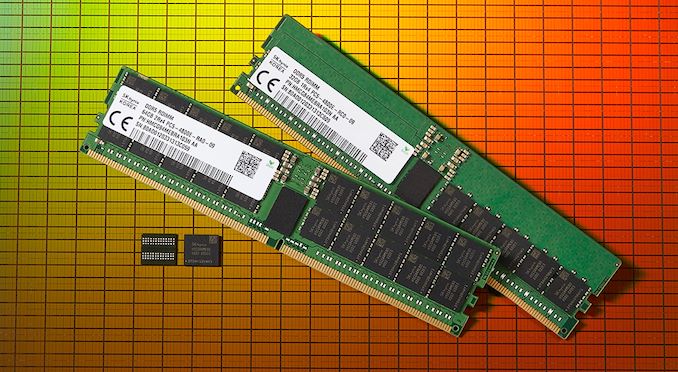

El anuncio de SK Hynix hoy es que están listos para comenzar a enviar memoria DDR5 ECC a los fabricantes de módulos, específicamente matrices de 16 gigabits construidas en su proceso de 1 minuto que admiten DDR5 – 4800 a DDR5-5600 a 1,1 voltios. Con la tecnología de embalaje adecuada (como TSV 3D), SK Hynix dice que los socios pueden construir discos LR de 256 GB. Los propios fabricantes de módulos tendrán que hacer un compartimiento adicional de los chips para obtener velocidades mejores que las del JEDEC. SK Hynix también parece tener sus propios módulos, específicamente RDIMM de 32 GB y 64 GB en DDR5-4800, y previamente ha prometido ofrecer memoria hasta DDR5-8400.

SK Hynix no ha facilitado información sobre los tiempos parciales de estos módulos. La especificación JEDEC define tres modos diferentes para DDR5-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B: 40-40-40

- DDR5-4800C: 42-42-42

No está claro cuál de estos está utilizando SK Hynix. El módulo dice ‘4800E’, sin embargo, eso parece ser solo parte del nombre del módulo, ya que la especificación JEDEC no va más allá de un valor CL de 42 para DDR5-4800.

Para el ancho de banda, otros fabricantes de memoria han citado que para los 38,4 GB/s teóricos que cada módulo de DDR5-4800 puede traer, ya están viendo números efectivos en el rango de 32 GB/s. Esto está por encima de los 20-25 GB/s efectivos por canal que estamos viendo en DDR4-3200 hoy. Otros fabricantes de memorias ya han anunciado que están muestreando DDR5 con clientes desde principios de año.

Como parte del anuncio, fue interesante ver a Intel como uno de los socios principales para estos módulos. Intel se ha comprometido a habilitar DDR5 en su plataforma de procesadores Sapphire Rapids Xeon, cuyo lanzamiento inicial está previsto para finales de 2021/2022. AMD no fue mencionado en el anuncio, y tampoco lo fueron los socios de Arm.

SK Hynix cita que se espera que DDR5 sea el 10% del mercado mundial en 2022, aumentando al 43% en 2024. El punto de intersección para las plataformas de consumo está algo borroso en este punto, ya que probablemente solo estemos a mitad de camino (o menos de la mitad) del ciclo DDR4. Tradicionalmente, esperamos una interceptación de costos entre la tecnología antigua y la nueva cuando tienen la misma cuota de mercado, sin embargo, es probable que los costos adicionales en la regulación de voltaje que requiere DDR5 aumenten los costos de los módulos, escalando desde la entrega de energía estándar en los módulos JEDEC hasta una solución más sólida en los módulos con overclock. Sin embargo, debería abaratar las placas base en ese sentido.

Fuente: SK hynix

Lectura relacionada

- Especificación de memoria DDR5 Lanzada: Preparando el escenario para DDR5-6400 Y Más Allá

- SK Hynix: Estamos planeando para DDR5-8400 en 1.Actualización DDR5 de cadencia de 1 Voltios

- : Lanzamiento a 4800 MT/s, Más de 12 SoCs DDR5 en desarrollo

- Samsung para producir DDR5 en 2021 (con EUV)

- Aquí hay un poco de DDR5-4800: Primer vistazo práctico a la DRAM de próxima generación

- CES 2020: Micron Comienza a Muestra de RDIMMs DDR5 con socios de servidor

- SK Hynix Detalles DDR5-6400

- Keysight Revela Pruebas de DDR5 & Sistema de Validación

- SK Hynix Desarrolla El Primer Chip de Memoria DDR5-5200 de 16 Gb, Demostraciones DDR5 RDIMM

- Cadencia & Micras Actualización de DDR5: Chips de 16 Gb en marcha para 2019

- Cadencia y Micron Demo DDR5-4400 IMC y Memoria, Con fecha de entrega en 2019