a DDR memória következő generációjának megvitatása az elmúlt hónapokban zavaros volt, mivel a gyártók sokféle tesztjárművet mutattak be a teljes termék bevezetése előtt. A DDR5 használatát tervező platformok szintén gyorsan közelednek, várhatóan debütálnak a vállalati oldalon, mielőtt lassan lecsapnának a fogyasztókra. Mint minden ilyen dolog, a fejlesztés szakaszokban történik: memóriavezérlők, interfészek, elektromos egyenértékű vizsgálati IP és modulok. Ez az utolsó szakasz, amelyet az SK Hynix ma indít, vagy legalábbis a chipek, amelyek ezekbe a modulokba kerülnek.

a DDR5 a platformmemória következő szakasza a főbb számítási platformok többségében. A specifikáció (2020 júliusában jelent meg) a főfeszültséget 1,2 V-ról 1,1 V-ra csökkenti, 4-szeresére növeli a maximális Szilícium szerszámsűrűséget, megduplázza a maximális adatátviteli sebességet, megduplázza a sorozathosszt és megduplázza a bankcsoportok számát. Egyszerűen fogalmazva, a JEDEC DDR specifikációk lehetővé teszik egy 128 GB-os puffer nélküli modul futtatását a DDR5-6400-on. RDIMMs és LRDIMMs képesnek kell lennie arra, hogy menjen sokkal magasabb, teljesítmény lehetővé teszi.

a DDR világában négy szög van, amelyeken mindenki, aki részt vesz a specifikációban, meg akarja ismételni. A kapacitás nyilvánvaló, de a memória sávszélessége is kulcsszerepet játszik a közös többmagos munkaterhelések teljesítménymérésében az általunk látott nagy magszámú szerverekben. A másik kettő hatalom (nyilvánvaló cél), a másik pedig a késleltetés, a teljesítmény másik kulcsfontosságú mutatója.

a DDR5-tel az egyik legfontosabb változás, amely segít a meghajtásban, az, ahogyan a rendszer látja a memóriát. Ahelyett, hogy modulonként egyetlen 64 bites adatcsatorna lenne, a DDR5 modulonként két 32 bites adatcsatornának tekinthető (vagy 40 bit ECC-ben). A sorozat hossza megduplázódott, ami azt jelenti, hogy minden 32 bites csatorna továbbra is 64 bájtot fog szolgáltatni műveletenként, de ezt jobban átlapolhatja. Ez azt jelenti, hogy a standard ‘két 64 bites csatorna DDR4’ rendszer átalakul egy ‘quad 32 bites csatorna DDR5’ elrendezéssé, bár mindegyik memory stick összesen 64 bites, de jobban szabályozható módon. Ez megkönnyíti az adatátviteli sebesség megduplázását is, amely kulcsfontosságú elem a csúcs sávszélességének növelésében, valamint egy finomabb szemcsés banki frissítési funkciót, amely lehetővé teszi az aszinkron műveleteket a memóriában használat közben, csökkentve a késleltetést.

a feszültségszabályozás az alaplapról a memóriamodulra is átkerül, lehetővé téve a modul számára a saját igényeinek szabályozását. Már láttuk, hogy a DDR4 elfogadja a chipenkénti Vdroop vezérlést, de ez az egész ötletet egy lépéssel tovább viszi a szigorúbb teljesítményszabályozás és-kezelés érdekében. Ezenkívül az energiagazdálkodást a modulgyártó, nem pedig az alaplap gyártója kezébe adja, lehetővé téve a modulgyártó számára, hogy méretezze a gyorsabb memóriához szükséges méretet – érdekes lesz látni, hogy a különböző firmware hogyan képes megbirkózni a nem JEDEC szabványos játékmemóriával, amely kétségtelenül meghaladja a specifikációt.

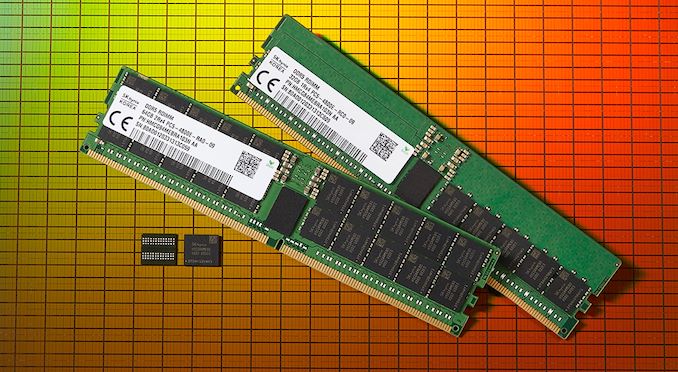

az SK Hynix ma bejelentette, hogy készen állnak a DDR5 ECC memória szállításának megkezdésére a modulgyártók számára – konkrétan 16 gigabites meghal, amely az 1Ynm folyamatára épül, amely támogatja a DDR5-4800-DDR5-5600-at 1, 1 voltos feszültséggel. A megfelelő csomagolási technológiával (például 3D TSV) az SK Hynix szerint a partnerek 256 GB-os LRDIMM-eket építhetnek. A chipek további binningjét a JEDECNÉL jobb sebesség érdekében maguknak a modulgyártóknak kell elvégezniük. Úgy tűnik, hogy az SK Hynix saját modulokkal is rendelkezik, különösen a 32 GB-os és a 64 GB-os RDIMM-ekkel a DDR5-4800-nál, és korábban megígérte, hogy DDR5-8400-as memóriát kínál.

az SK Hynix nem szolgáltatott információt e modulok időzítéséről. A JEDEC specifikáció három különböző módot határoz meg a DDR5 számára-4800:

- DDR5-4800A: 34-34-34

- DDR5-4800B: 40-40-40

- DDR5-4800C: 42-42-42

nem világos, hogy ezek közül melyiket használja az SK Hynix. A modul azt mondja ,hogy ‘4800E’, azonban úgy tűnik, hogy csak a modul elnevezésének része, mivel a JEDEC specifikáció nem haladja meg a 42 CL értéket a DDR5-4800 esetében.

a sávszélesség tekintetében más memóriagyártók idézték, hogy az elméleti 38, 4 GB/s-hoz, amelyet a DDR5-4800 minden modulja hozhat, már látják a tényleges számokat a 32 GB/s tartományban. Ez meghaladja a csatornánkénti tényleges 20-25 GB/s értéket, amelyet ma a DDR4-3200-on látunk. Más memóriagyártók már bejelentették, hogy az év eleje óta mintavételezik a DDR5-et az ügyfelekkel.

a bejelentés részeként érdekes volt látni, hogy az Intel a modulok egyik vezető partnere. Az Intel elkötelezte magát amellett, hogy engedélyezi a DDR5-et a Sapphire Rapids Xeon processzorplatformján, amelynek első bevezetése 2021/2022 végén várható. Az AMD-t nem említették a bejelentésben, és Arm partnerek sem voltak.

az SK Hynix idézi, hogy a DDR5 várhatóan a globális piac 10% – át teszi ki 2022-ben, 43% – ra növekszik 2024-ben. A fogyasztói platformok metszéspontja ezen a ponton kissé homályos, mivel valószínűleg csak a DDR4 ciklus felénél (vagy kevesebb mint felénél) vagyunk. Hagyományosan arra számítunk, hogy a régi és az új technológia közötti költségmegszakítás egyenlő piaci részesedéssel jár, azonban a feszültségszabályozás többletköltségei, amelyeket a DDR5 igényel, valószínűleg növelik a modulköltségeket – a JEDEC modulok szabványos áramellátásától a túlhajtott modulok beefier megoldásáig. E tekintetben azonban olcsóbbá kell tennie az alaplapokat.

forrás: SK hynix

kapcsolódó olvasás

- megjelent a DDR5 memória specifikáció: a színpad beállítása a DDR5-6400 és azon túl

- SK Hynix: a DDR5-8400 at 1-et tervezzük.1 volt

- Cadence DDR5 frissítés: 4800 MT/s sebességgel indul, több mint 12 DDR5 Soc fejlesztés alatt

- a Samsung a DDR5 gyártását 2021-ben (EUV-vel)

- íme néhány DDR5-4800: gyakorlati első pillantás a következő generációs DRAM-ra

- CES 2020: a Micron elkezdi a DDR5 gyártását minta DDR5 RDIMM szerver partnerekkel

- SK Hynix részletek DDR5-6400

- Keysight feltárja DDR5 tesztelés & érvényesítési rendszer

- SK Hynix fejleszti első 16 GB DDR5-5200 Memória Chip, demók DDR5 RDIMM

- Cadence & Mikron DDR5 frissítés: 16 Gb-os chipek a pályán 2019-re

- Cadence és Micron Demo DDR5 – 4400 IMC és memória, 2019-ben esedékes