VHDL står for meget høj hastighed integreret kredsløb beskrivelse sprog. Det er et programmeringssprog, der bruges til at modellere et digitalt system efter datastrøm, adfærdsmæssig og strukturel modelleringsstil. Dette sprog blev først introduceret i 1981 for forsvarsministeriet (DoD) under VHSIC-programmet.

beskrivelse af et Design

i VHDL bruges en enhed til at beskrive et udstyrsmodul. En enhed kan beskrives ved hjælp af,

- enhedserklæring

- arkitektur

- konfiguration

- Pakkedeklaration

- Pakkekrop

lad os se, hvad er disse?

Enhedserklæring

det definerer navne, input udgangssignaler og tilstande for et udstyrsmodul.

syntaks−

entity entity_name is Port declaration;end entity_name;

en enhedserklæring skal starte med’ enhed ‘og slutte med’ Slut ‘ nøgleord. Retningen vil være input, output eller inout.

| i | Port kan læses |

| ud | Port kan skrives |

| Inout | Port kan læses og skrives |

| Buffer | Port kan læses og skrives, den kan kun have en kilde. |

arkitektur –

arkitektur kan beskrives ved hjælp af strukturel, dataforløb, adfærdsmæssig eller blandet stil.

syntaks−

architecture architecture_name of entity_name architecture_declarative_part;begin Statements;end architecture_name;

her skal vi angive det enhedsnavn, som vi skriver arkitekturorganet for. Arkitekturerklæringerne skal være inde i nøgleordet’ begin’ og ‘Purpur’. Arkitektur deklarativ del kan indeholde variabler, konstanter eller komponenterklæring.

Datastrømsmodellering

i denne modelleringsstil udtrykkes strømmen af data gennem enheden ved hjælp af samtidigt (parallelt) signal. De samtidige udsagn i VHDL er hvornår og generere.

udover dem, opgaver, der kun bruger operatører (og ikke & plus;,*, sll osv.) kan også bruges til at konstruere kode.

endelig kan en særlig form for opgave, kaldet blok, også anvendes i denne type kode.

i samtidig kode kan følgende bruges−

- operatorer

- når-sætningen (når/ellers eller med/Vælg/hvornår);

- generer-sætningen;

- Bloker sætningen

Adfærdsmodellering

i denne modelleringsstil udføres en enheds adfærd som sæt af udsagn sekventielt i den angivne rækkefølge. Kun udsagn placeret i en proces, funktion eller PROCEDURE er sekventielle.

processer, funktioner og procedurer er de eneste kodesektioner, der udføres sekventielt.

men som helhed er nogen af disse blokke stadig samtidig med andre udsagn placeret uden for den.

et vigtigt aspekt af adfærdskode er, at det ikke er begrænset til sekventiel logik. Faktisk kan vi med det Bygge sekventielle kredsløb såvel som kombinationskredsløb.

adfærdserklæringerne er hvis, vent, sag og LOOP. Variabler er også begrænset, og de skal kun bruges i sekventiel kode. Variabel kan aldrig være global, så dens værdi kan ikke videregives direkte.

strukturel modellering

i denne modellering beskrives en enhed som et sæt sammenkoblede komponenter. En komponent instantiation erklæring er en samtidig erklæring. Derfor er rækkefølgen af disse udsagn ikke vigtig. Modelleringens strukturelle stil beskriver kun en sammenkobling af komponenter (betragtet som sorte kasser) uden at antyde nogen opførsel af komponenterne selv eller af den enhed, som de kollektivt repræsenterer.

i strukturel modellering er arkitekturkroppen sammensat af to dele − den deklarative del (før nøgleordet begynder) og udsagnsdelen (efter nøgleordet begynder).

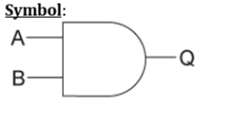

logisk drift – og GATE

| Y | å | |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

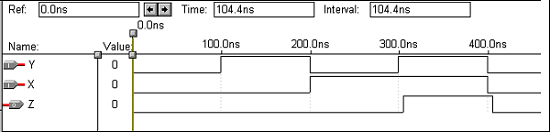

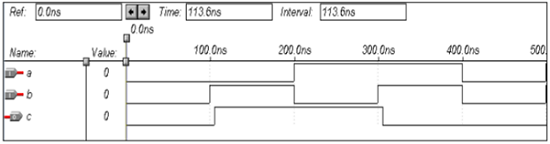

bølgeformer

Logic Operation – or Gate

| Y | å | |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

bølgeformer

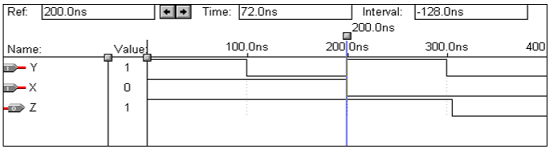

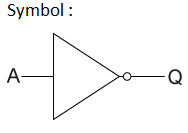

logisk drift – ikke Gate

| Y | |

|---|---|

| 0 | 1 |

| 1 | 0 |

bølgeformer

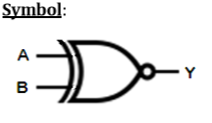

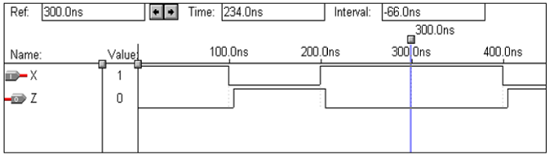

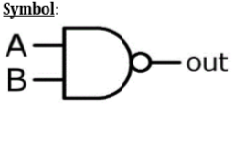

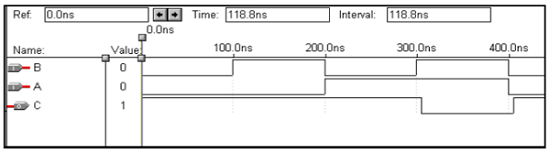

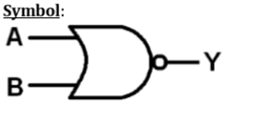

logisk drift – NAND Gate

| Y | å | |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

bølgeformer

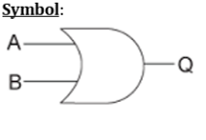

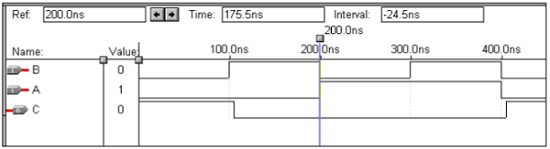

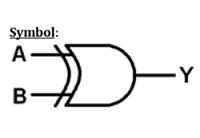

logisk drift-NOR Gate

| Y | å | |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

bølgeformer

Logic Operation

| Y | å | |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

bølgeformer

Logic Operation-NOR Gate